8086

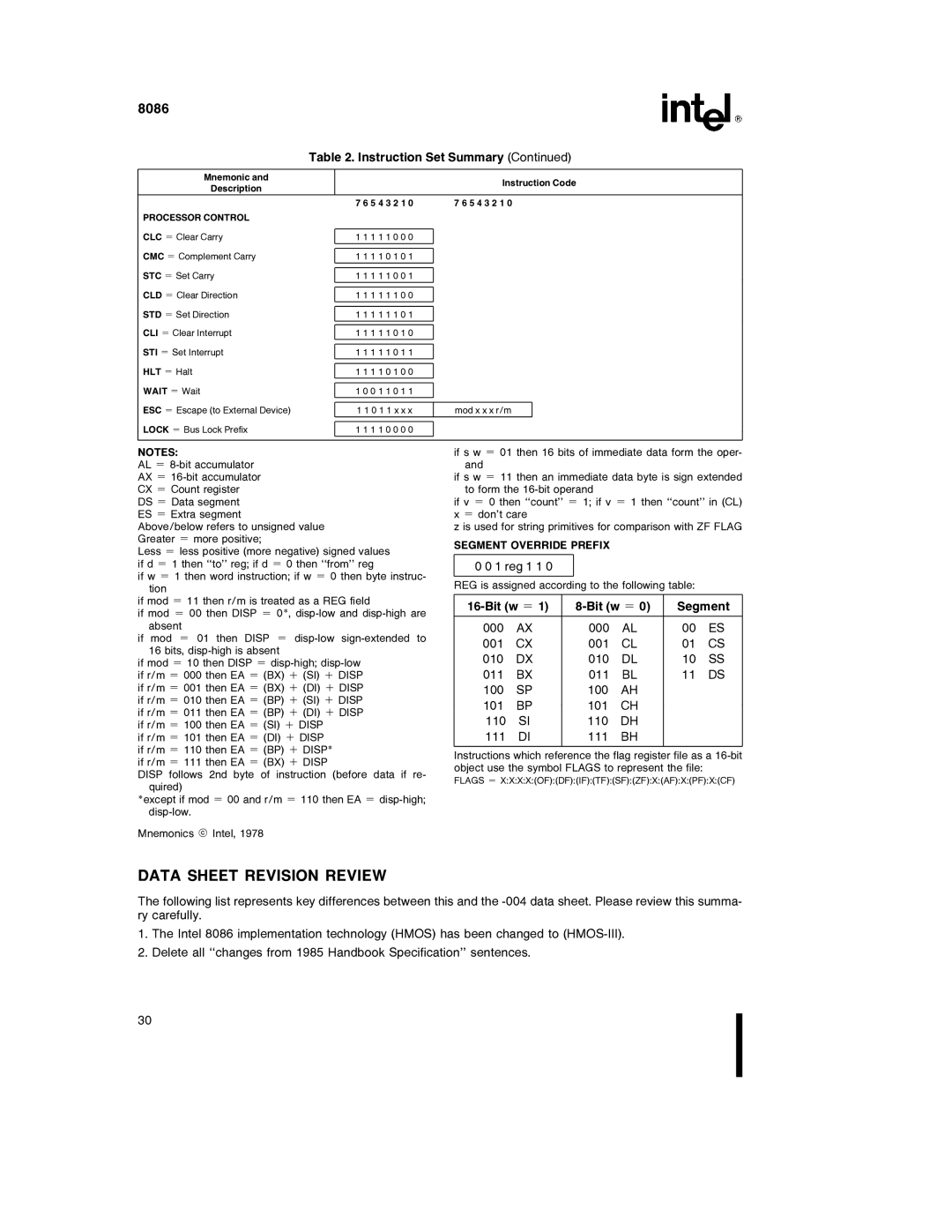

Table 2. Instruction Set Summary (Continued)

Mnemonic and | Instruction Code | |

Description | ||

|

| 7 6 5 4 3 2 1 0 | 7 6 5 4 3 2 1 0 |

PROCESSOR CONTROL |

|

|

CLC e Clear Carry |

|

|

1 1 1 1 1 0 0 0 |

| |

CMC e Complement Carry |

|

|

1 1 1 1 0 1 0 1 |

| |

STC e Set Carry |

|

|

1 1 1 1 1 0 0 1 |

| |

CLD e Clear Direction |

|

|

1 1 1 1 1 1 0 0 |

| |

STD e Set Direction |

|

|

1 1 1 1 1 1 0 1 |

| |

CLI e Clear Interrupt | 1 1 1 1 1 0 1 0 |

|

STI e Set Interrupt |

|

|

1 1 1 1 1 0 1 1 |

| |

HLT e Halt |

|

|

1 1 1 1 0 1 0 0 |

| |

WAIT e Wait |

|

|

1 0 0 1 1 0 1 1 |

| |

ESC e Escape (to External Device) |

|

|

1 1 0 1 1 x x x | mod x x x r/m | |

LOCK e Bus Lock Prefix |

|

|

1 1 1 1 0 0 0 0 |

|

NOTES:

AL e

Above/below refers to unsigned value Greater e more positive;

Less e less positive (more negative) signed values if d e 1 then ‘‘to’’ reg; if d e 0 then ‘‘from’’ reg

if w e 1 then word instruction; if w e 0 then byte instruc- tion

if mod e 11 then r/m is treated as a REG field

if mod e 00 then DISP e 0*,

if mod e 01 then DISP e

if mod e 10 then DISP e

if r/m e 101 then EA e (DI) a DISP if r/m e 110 then EA e (BP) a DISP* if r/m e 111 then EA e (BX) a DISP

DISP follows 2nd byte of instruction (before data if re- quired)

*except if mod e 00 and r/m e 110 then EA e

Mnemonics ' Intel, 1978

if s w e 01 then 16 bits of immediate data form the oper- and

if s w e 11 then an immediate data byte is sign extended to form the

if v e 0 then ‘‘count’’ e 1; if v e 1 then ‘‘count’’ in (CL) x e don’t care

z is used for string primitives for comparison with ZF FLAG SEGMENT OVERRIDE PREFIX

0 0 1 reg 1 1 0

REG is assigned according to the following table:

| Segment | ||||

000 | AX | 000 | AL | 00 | ES |

001 | CX | 001 | CL | 01 | CS |

010 | DX | 010 | DL | 10 | SS |

011 | BX | 011 | BL | 11 | DS |

100 | SP | 100 | AH |

|

|

101 | BP | 101 | CH |

|

|

110 | SI | 110 | DH |

|

|

111 | DI | 111 | BH |

|

|

|

|

|

|

|

|

Instructions which reference the flag register file as a

FLAGS e X:X:X:X:(OF):(DF):(IF):(TF):(SF):(ZF):X:(AF):X:(PF):X:(CF)

DATA SHEET REVISION REVIEW

The following list represents key differences between this and the

1.The Intel 8086 implementation technology (HMOS) has been changed to

2.Delete all ‘‘changes from 1985 Handbook Specification’’ sentences.

30