MASKABLE INTERRUPT (INTR)

The 8086 provides a single interrupt request input (INTR) which can be masked internally by software with the resetting of the interrupt enable FLAG status bit. The interrupt request signal is level trig- gered. It is internally synchronized during each clock cycle on the

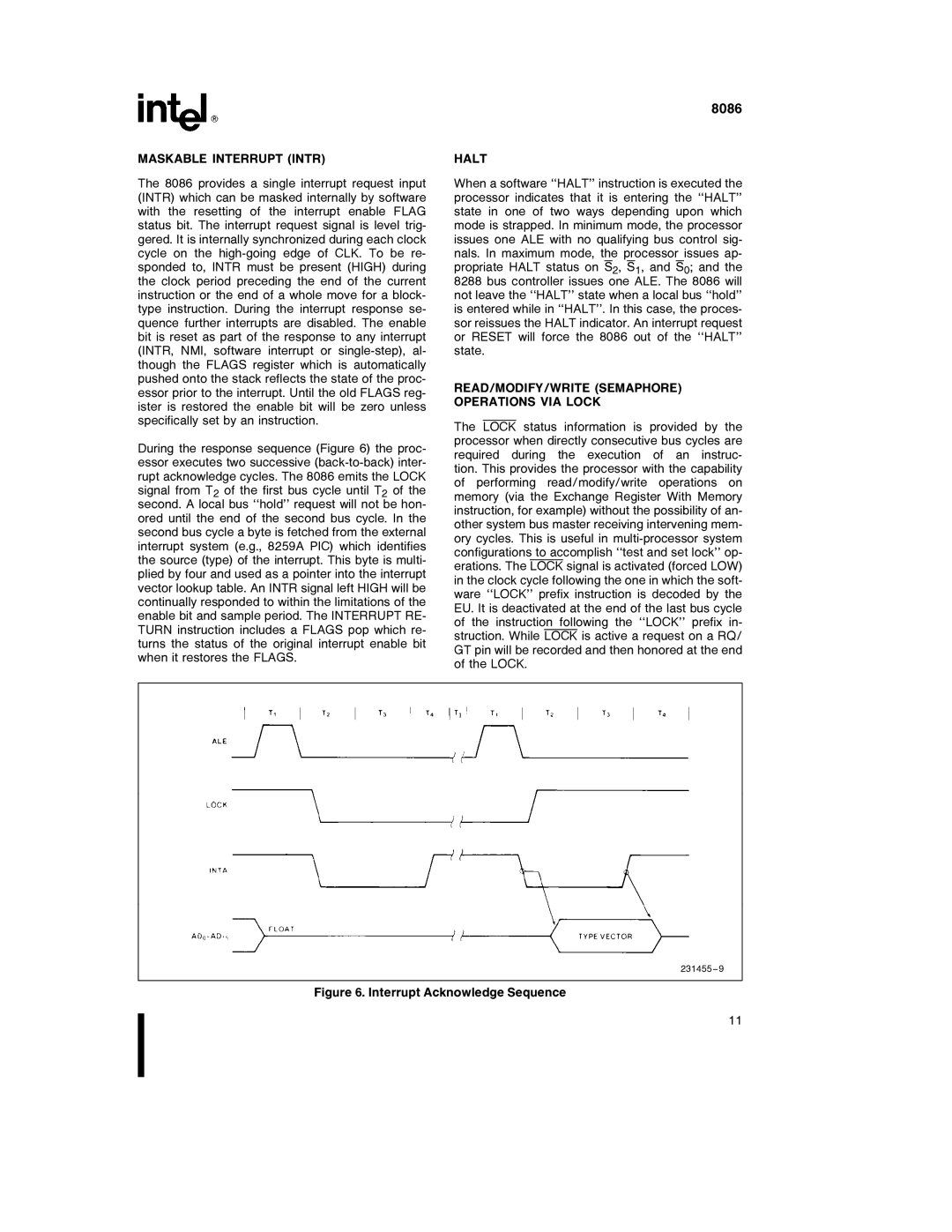

During the response sequence (Figure 6) the proc- essor executes two successive

8086

HALT

When a software ‘‘HALT’’ instruction is executed the processor indicates that it is entering the ‘‘HALT’’ state in one of two ways depending upon which mode is strapped. In minimum mode, the processor issues one ALE with no qualifying bus control sig- nals. In maximum mode, the processor issues ap- propriate HALT status on S2, S1, and S0; and the 8288 bus controller issues one ALE. The 8086 will not leave the ‘‘HALT’’ state when a local bus ‘‘hold’’ is entered while in ‘‘HALT’’. In this case, the proces- sor reissues the HALT indicator. An interrupt request or RESET will force the 8086 out of the ‘‘HALT’’ state.

READ/MODIFY/WRITE (SEMAPHORE) OPERATIONS VIA LOCK

The LOCK status information is provided by the processor when directly consecutive bus cycles are required during the execution of an instruc- tion. This provides the processor with the capability of performing read/modify/write operations on memory (via the Exchange Register With Memory instruction, for example) without the possibility of an- other system bus master receiving intervening mem- ory cycles. This is useful in

231455 – 9

Figure 6. Interrupt Acknowledge Sequence

11