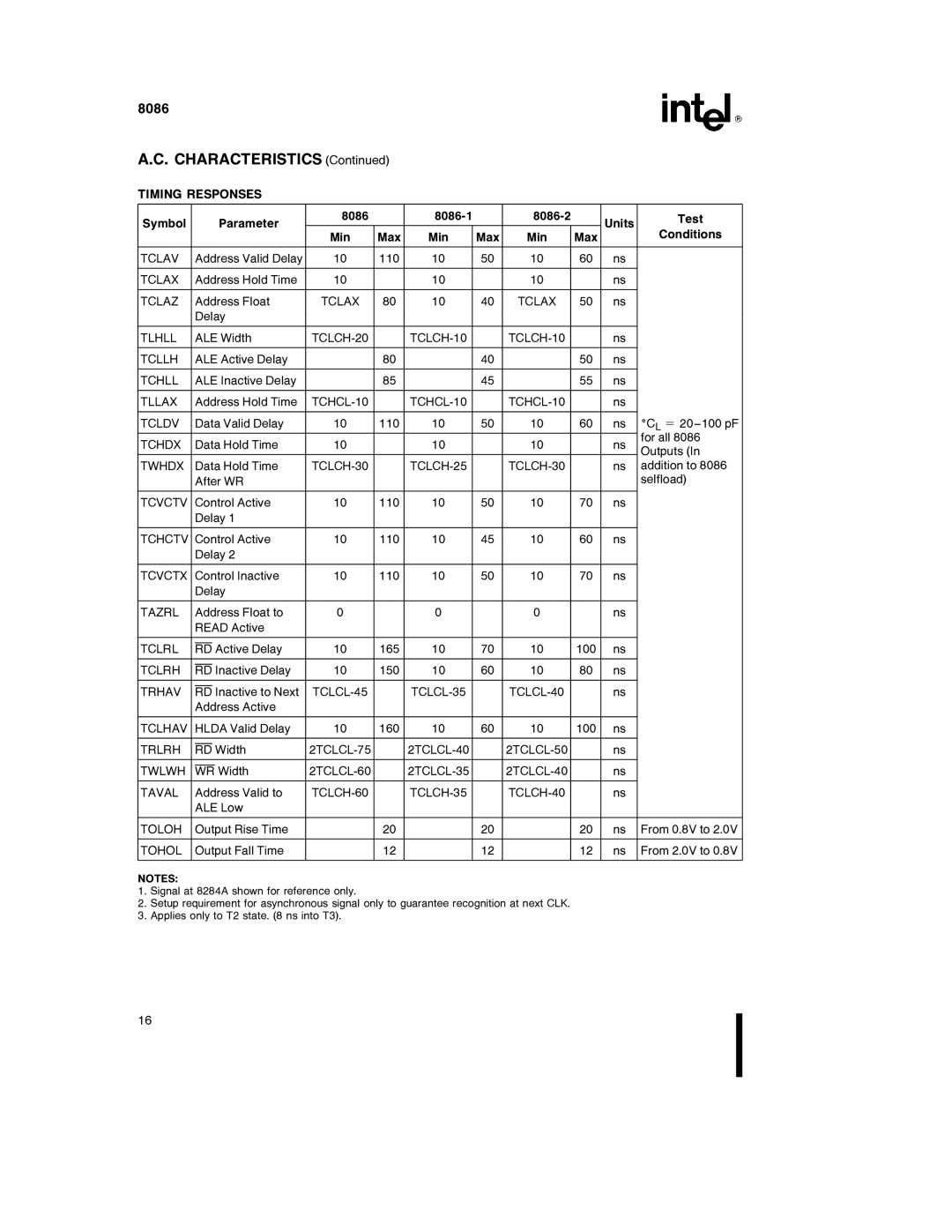

8086

A.C. CHARACTERISTICS (Continued)

TIMING RESPONSES

Symbol |

|

|

| Parameter | 8086 |

|

|

| Units | Test | ||

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

| Min | Max | Min | Max | Min | Max |

| Conditions |

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

TCLAV | Address Valid Delay | 10 | 110 | 10 | 50 | 10 | 60 | ns |

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

TCLAX | Address Hold Time | 10 |

| 10 |

| 10 |

| ns |

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

TCLAZ | Address Float | TCLAX | 80 | 10 | 40 | TCLAX | 50 | ns |

| |||

| Delay |

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

TLHLL | ALE Width |

|

|

| ns |

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

TCLLH | ALE Active Delay |

| 80 |

| 40 |

| 50 | ns |

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

TCHLL | ALE Inactive Delay |

| 85 |

| 45 |

| 55 | ns |

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

TLLAX | Address Hold Time |

|

|

| ns |

| ||||||

|

|

|

|

|

|

|

|

|

|

|

| *CL e 20 – 100 pF |

TCLDV | Data Valid Delay | 10 | 110 | 10 | 50 | 10 | 60 | ns | ||||

TCHDX | Data Hold Time | 10 |

| 10 |

| 10 |

| ns | for all 8086 | |||

|

|

| Outputs (In | |||||||||

|

|

|

|

|

|

|

|

|

|

|

| |

TWHDX | Data Hold Time |

|

|

| ns | addition to 8086 | ||||||

| After WR |

|

|

|

|

|

|

| selfload) | |||

|

|

|

|

|

|

|

|

|

|

|

|

|

TCVCTV | Control Active | 10 | 110 | 10 | 50 | 10 | 70 | ns |

| |||

| Delay 1 |

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

TCHCTV | Control Active | 10 | 110 | 10 | 45 | 10 | 60 | ns |

| |||

| Delay 2 |

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

TCVCTX | Control Inactive | 10 | 110 | 10 | 50 | 10 | 70 | ns |

| |||

| Delay |

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

TAZRL | Address Float to | 0 |

| 0 |

| 0 |

| ns |

| |||

| READ Active |

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TCLRL | RD Active Delay | 10 | 165 | 10 | 70 | 10 | 100 | ns |

| |||

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

TCLRH | RD Inactive Delay | 10 | 150 | 10 | 60 | 10 | 80 | ns |

| |||

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

TRHAV | RD Inactive to Next |

|

|

| ns |

| ||||||

| Address Active |

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

| |

TCLHAV | HLDA Valid Delay | 10 | 160 | 10 | 60 | 10 | 100 | ns |

| |||

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

TRLRH | RD Width |

|

|

| ns |

| ||||||

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

| |

TWLWH | WR Width |

|

|

| ns |

| ||||||

|

|

|

|

|

|

|

|

|

| |||

TAVAL | Address Valid to |

|

|

| ns |

| ||||||

| ALE Low |

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

| |||

TOLOH | Output Rise Time |

| 20 |

| 20 |

| 20 | ns | From 0.8V to 2.0V | |||

|

|

|

|

|

|

|

|

|

| |||

TOHOL | Output Fall Time |

| 12 |

| 12 |

| 12 | ns | From 2.0V to 0.8V | |||

|

|

|

|

|

|

|

|

|

|

|

|

|

NOTES:

1.Signal at 8284A shown for reference only.

2.Setup requirement for asynchronous signal only to guarantee recognition at next CLK.

3.Applies only to T2 state. (8 ns into T3).

16