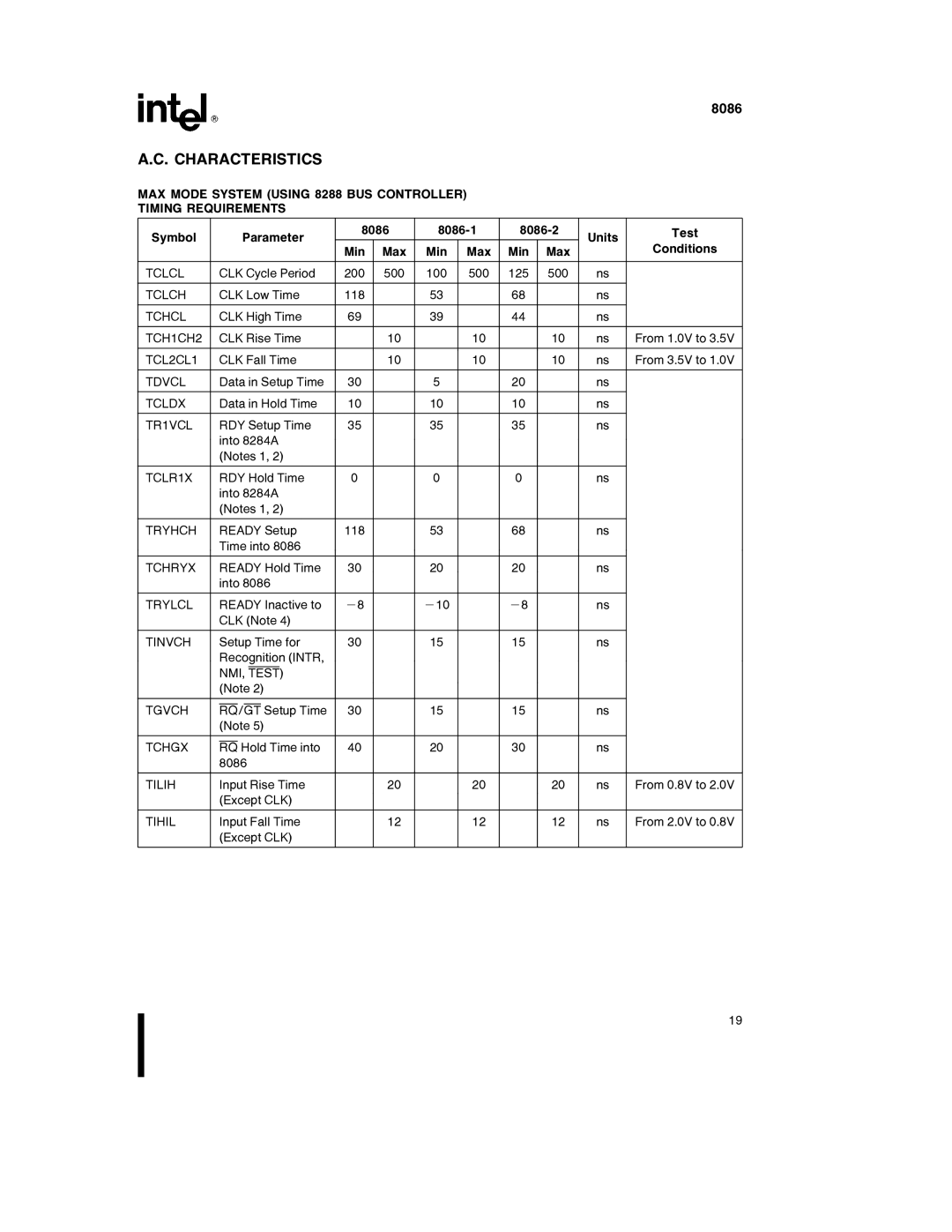

8086

A.C. CHARACTERISTICS

MAX MODE SYSTEM (USING 8288 BUS CONTROLLER)

TIMING REQUIREMENTS

Symbol |

|

| Parameter | 8086 | Units | Test | |||||||||

|

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

| Min | Max | Min | Max | Min | Max |

| Conditions |

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TCLCL | CLK Cycle Period | 200 | 500 | 100 | 500 | 125 | 500 | ns |

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TCLCH | CLK Low Time | 118 |

| 53 |

| 68 |

| ns |

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TCHCL | CLK High Time | 69 |

| 39 |

| 44 |

| ns |

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TCH1CH2 | CLK Rise Time |

| 10 |

| 10 |

| 10 | ns | From 1.0V to 3.5V | ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TCL2CL1 | CLK Fall Time |

| 10 |

| 10 |

| 10 | ns | From 3.5V to 1.0V | ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TDVCL | Data in Setup Time | 30 |

| 5 |

| 20 |

| ns |

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TCLDX | Data in Hold Time | 10 |

| 10 |

| 10 |

| ns |

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TR1VCL | RDY Setup Time | 35 |

| 35 |

| 35 |

| ns |

| ||||||

| into 8284A |

|

|

|

|

|

|

|

| ||||||

| (Notes 1, 2) |

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TCLR1X | RDY Hold Time | 0 |

| 0 |

| 0 |

| ns |

| ||||||

| into 8284A |

|

|

|

|

|

|

|

| ||||||

| (Notes 1, 2) |

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TRYHCH | READY Setup | 118 |

| 53 |

| 68 |

| ns |

| ||||||

| Time into 8086 |

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TCHRYX | READY Hold Time | 30 |

| 20 |

| 20 |

| ns |

| ||||||

| into 8086 |

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TRYLCL | READY Inactive to | b8 |

| b10 |

| b8 |

| ns |

| ||||||

| CLK (Note 4) |

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TINVCH | Setup Time for | 30 |

| 15 |

| 15 |

| ns |

| ||||||

| Recognition (INTR, |

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| NMI, TEST) |

|

|

|

|

|

|

|

| ||||||

| (Note 2) |

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

TGVCH | RQ/GT Setup Time | 30 |

| 15 |

| 15 |

| ns |

| ||||||

| (Note 5) |

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

| ||||

TCHGX | RQ Hold Time into | 40 |

| 20 |

| 30 |

| ns |

| ||||||

| 8086 |

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

| ||||||

TILIH | Input Rise Time |

| 20 |

| 20 |

| 20 | ns | From 0.8V to 2.0V | ||||||

| (Except CLK) |

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

| ||||||

TIHIL | Input Fall Time |

| 12 |

| 12 |

| 12 | ns | From 2.0V to 0.8V | ||||||

| (Except CLK) |

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

19