Watchdog timer setup

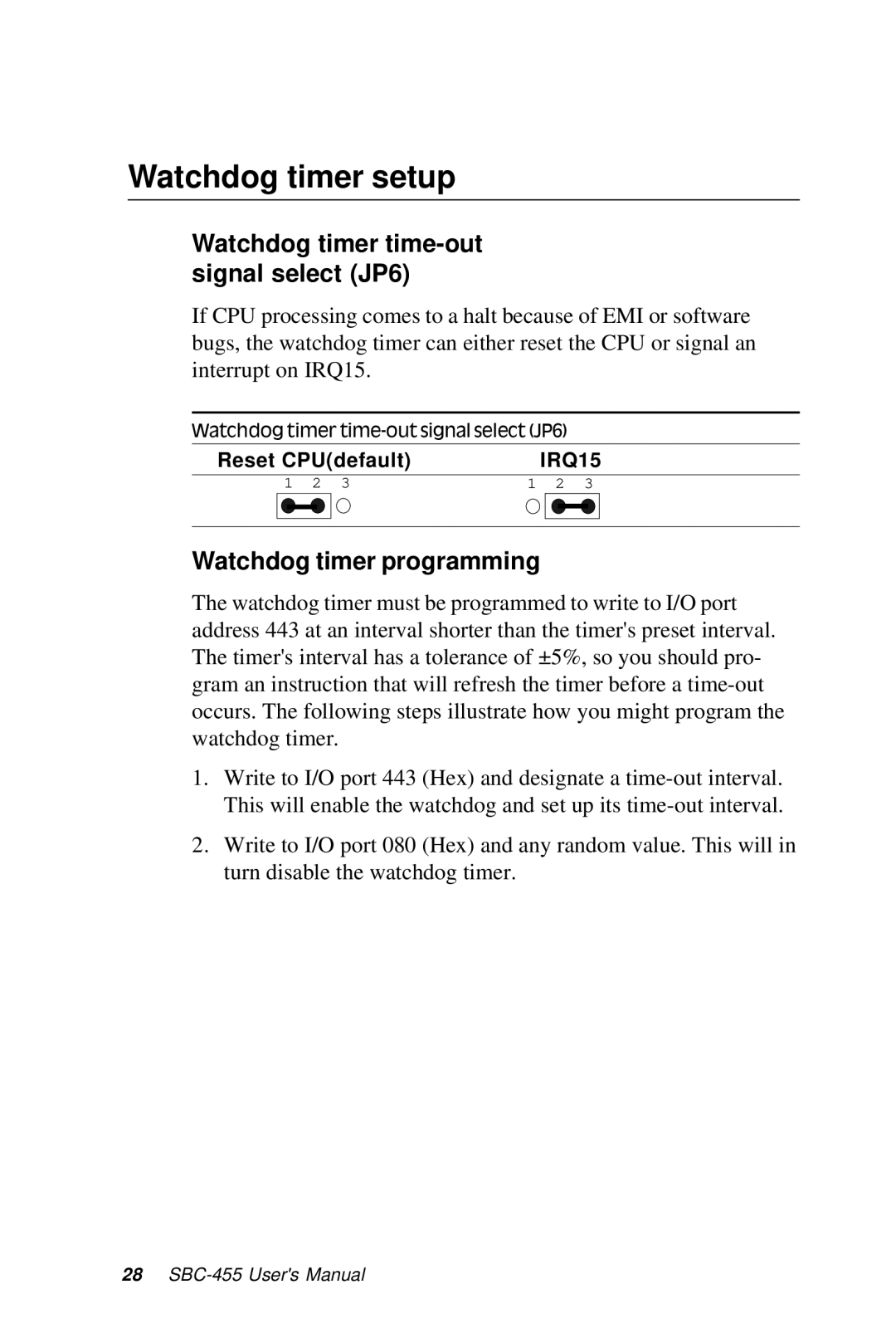

Watchdog timer time-out signal select (JP6)

If CPU processing comes to a halt because of EMI or software bugs, the watchdog timer can either reset the CPU or signal an interrupt on IRQ15.

Watchdog timer

Reset CPU(default) |

| IRQ15 | ||||||||

1 | 2 | 3 | 1 | 2 | 3 | |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Watchdog timer programming

The watchdog timer must be programmed to write to I/O port address 443 at an interval shorter than the timer's preset interval. The timer's interval has a tolerance of ±5%, so you should pro- gram an instruction that will refresh the timer before a

1.Write to I/O port 443 (Hex) and designate a

2.Write to I/O port 080 (Hex) and any random value. This will in turn disable the watchdog timer.

28