2.68254 Timer/Counter

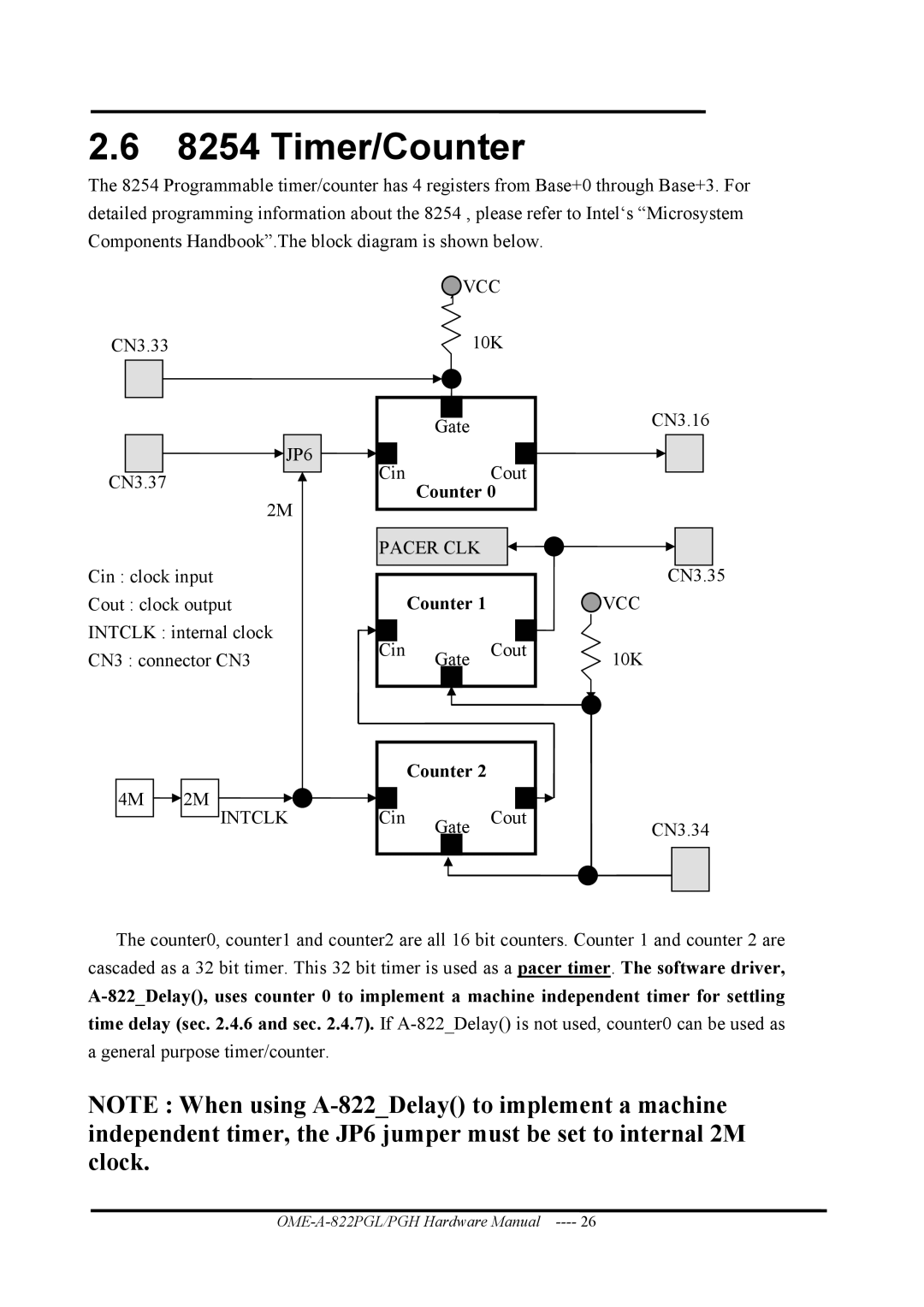

The 8254 Programmable timer/counter has 4 registers from Base+0 through Base+3. For detailed programming information about the 8254 , please refer to Intel‘s “Microsystem Components Handbook”.The block diagram is shown below.

![]() VCC

VCC

CN3.33 | 10K |

| JP6 |

CN3.37 | Cin |

| |

| 2M |

Gate |

Cout |

Counter 0 |

CN3.16

Cin : clock input

Cout : clock output

INTCLK : internal clock

CN3 : connector CN3

PACER CLK

Counter 1

Cin Gate Cout

CN3.35

![]() VCC

VCC

10K

4M ![]() 2M

2M

INTCLK

Counter 2

Cin Gate Cout

CN3.34

The counter0, counter1 and counter2 are all 16 bit counters. Counter 1 and counter 2 are cascaded as a 32 bit timer. This 32 bit timer is used as a pacer timer. The software driver,

a general purpose timer/counter.

NOTE : When using