www.ti.com

DDR2 Memory Controller Registers

4.6SDRAM Timing 2 Register (SDTIM2)

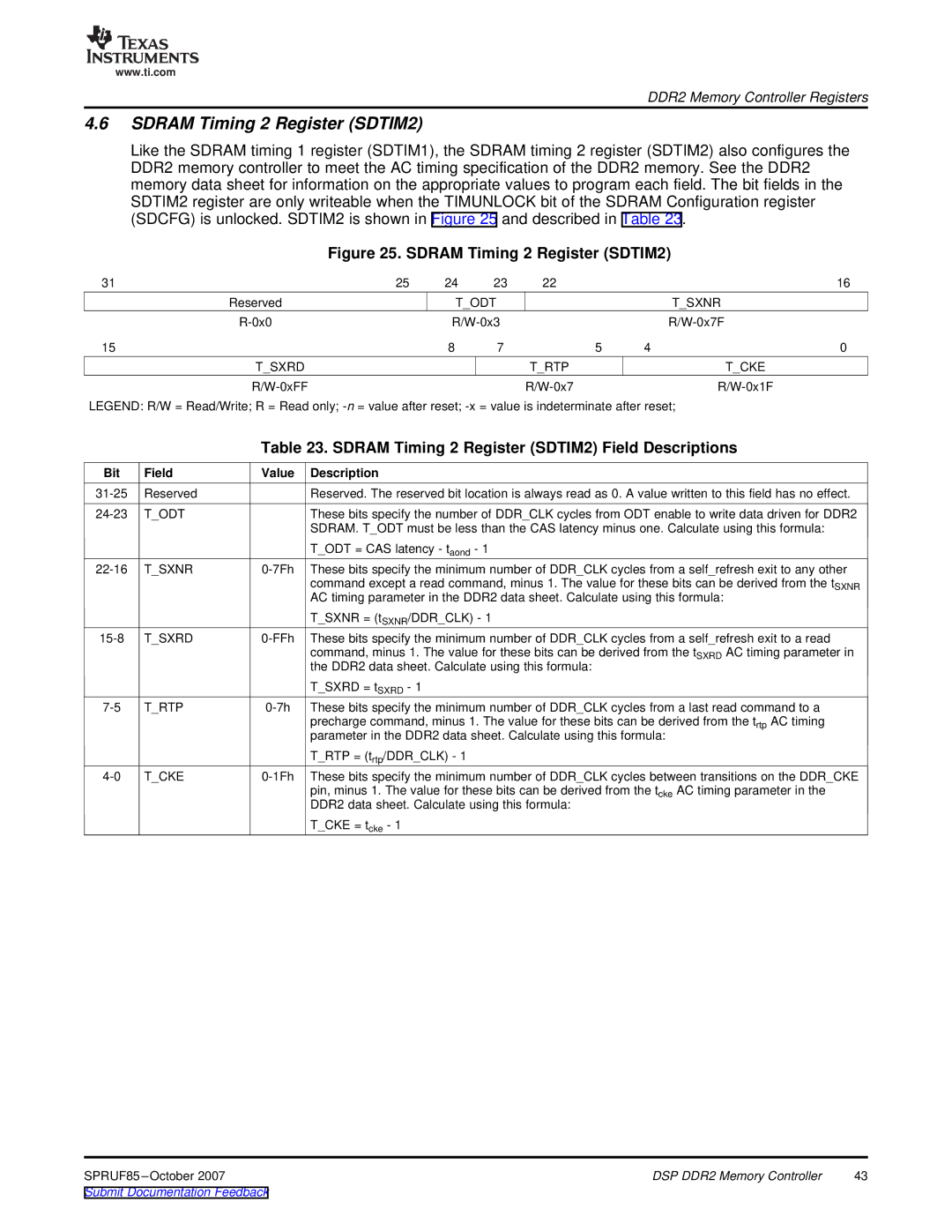

Like the SDRAM timing 1 register (SDTIM1), the SDRAM timing 2 register (SDTIM2) also configures the DDR2 memory controller to meet the AC timing specification of the DDR2 memory. See the DDR2 memory data sheet for information on the appropriate values to program each field. The bit fields in the SDTIM2 register are only writeable when the TIMUNLOCK bit of the SDRAM Configuration register (SDCFG) is unlocked. SDTIM2 is shown in Figure 25 and described in Table 23.

Figure 25. SDRAM Timing 2 Register (SDTIM2)

31 | 25 | 24 | 23 | 22 |

| 16 |

Reserved |

| T_ODT |

|

| T_SXNR | |

|

|

| ||||

15 |

| 8 | 7 | 5 | 4 | 0 |

T_SXRD |

|

|

| T_RTP |

| T_CKE |

|

|

|

| |||

LEGEND: R/W = Read/Write; R = Read only;

Table 23. SDRAM Timing 2 Register (SDTIM2) Field Descriptions

Bit | Field | Value | Description |

Reserved |

| Reserved. The reserved bit location is always read as 0. A value written to this field has no effect. | |

T_ODT |

| These bits specify the number of DDR_CLK cycles from ODT enable to write data driven for DDR2 | |

|

|

| SDRAM. T_ODT must be less than the CAS latency minus one. Calculate using this formula: |

|

|

| T_ODT = CAS latency - taond - 1 |

T_SXNR | These bits specify the minimum number of DDR_CLK cycles from a self_refresh exit to any other | ||

|

|

| command except a read command, minus 1. The value for these bits can be derived from the tSXNR |

|

|

| AC timing parameter in the DDR2 data sheet. Calculate using this formula: |

|

|

| T_SXNR = (tSXNR/DDR_CLK) - 1 |

T_SXRD | These bits specify the minimum number of DDR_CLK cycles from a self_refresh exit to a read | ||

|

|

| command, minus 1. The value for these bits can be derived from the tSXRD AC timing parameter in |

|

|

| the DDR2 data sheet. Calculate using this formula: |

|

|

| T_SXRD = tSXRD - 1 |

T_RTP | These bits specify the minimum number of DDR_CLK cycles from a last read command to a | ||

|

|

| precharge command, minus 1. The value for these bits can be derived from the trtp AC timing |

|

|

| parameter in the DDR2 data sheet. Calculate using this formula: |

|

|

| T_RTP = (trtp/DDR_CLK) - 1 |

T_CKE | These bits specify the minimum number of DDR_CLK cycles between transitions on the DDR_CKE | ||

|

|

| pin, minus 1. The value for these bits can be derived from the tcke AC timing parameter in the |

|

|

| DDR2 data sheet. Calculate using this formula: |

![]() T_CKE = tcke - 1

T_CKE = tcke - 1

SPRUF85 | DSP DDR2 Memory Controller | 43 |

Submit Documentation Feedback |

|

|