DSP_blk_eswap64

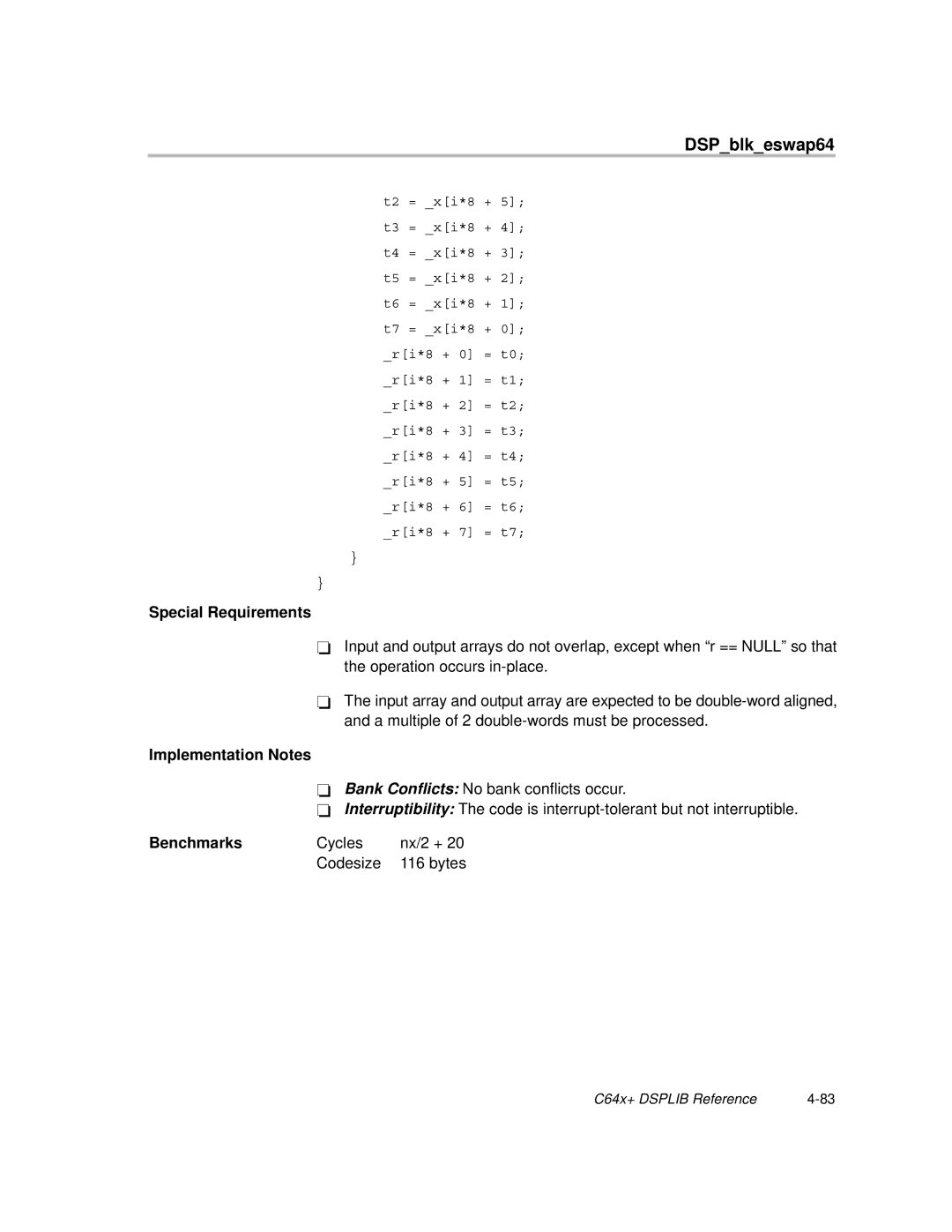

t2 = _x[i*8 + 5];

t3 = _x[i*8 + 4];

t4 = _x[i*8 + 3];

t5 = _x[i*8 + 2];

t6 = _x[i*8 + 1];

t7 = _x[i*8 + 0]; _r[i*8 + 0] = t0; _r[i*8 + 1] = t1; _r[i*8 + 2] = t2; _r[i*8 + 3] = t3; _r[i*8 + 4] = t4; _r[i*8 + 5] = t5; _r[i*8 + 6] = t6; _r[i*8 + 7] = t7;

}

}

Special Requirements

-Input and output arrays do not overlap, except when “r == NULL” so that the operation occurs

-The input array and output array are expected to be

Implementation Notes

| - Bank Conflicts: No bank conflicts occur. | |

| - Interruptibility: The code is | |

Benchmarks | Cycles | nx/2 + 20 |

| Codesize | 116 bytes |

C64x+ DSPLIB Reference |