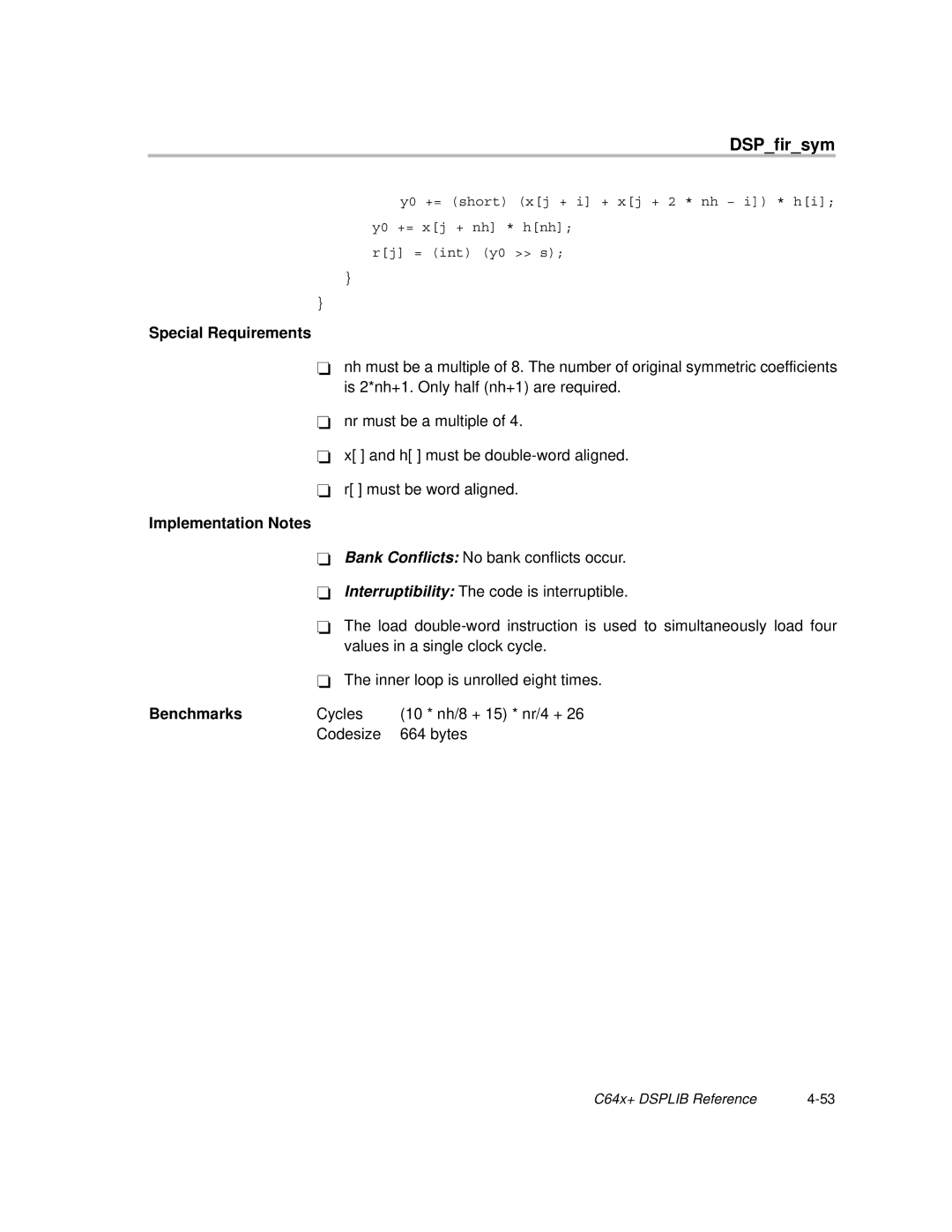

DSP_fir_sym

y0 += (short) (x[j + i] + x[j + 2 * nh − i]) * h[i];

y0 += x[j + nh] * h[nh];

r[j] = (int) (y0 >> s);

}

}

Special Requirements

-nh must be a multiple of 8. The number of original symmetric coefficients is 2*nh+1. Only half (nh+1) are required.

-nr must be a multiple of 4.

-x[ ] and h[ ] must be

-r[ ] must be word aligned.

Implementation Notes

| - Bank Conflicts: No bank conflicts occur. | |

| - Interruptibility: The code is interruptible. | |

| - The load | |

| values in a single clock cycle. | |

| - The inner loop is unrolled eight times. | |

Benchmarks | Cycles | (10 * nh/8 + 15) * nr/4 + 26 |

| Codesize | 664 bytes |

C64x+ DSPLIB Reference |