DSP_fft16x16r

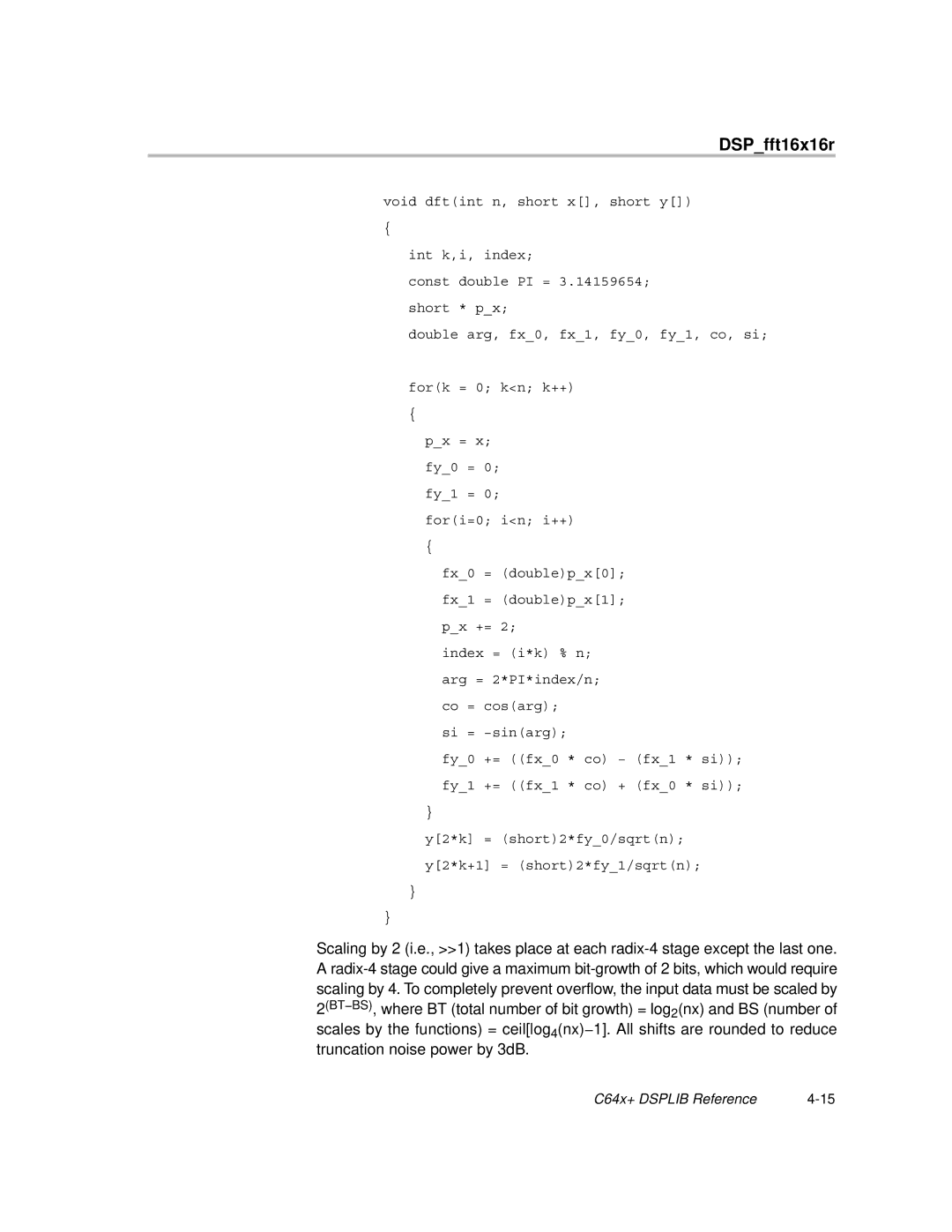

void dft(int n, short x[], short y[])

{

int k,i, index;

const double PI = 3.14159654; short * p_x;

double arg, fx_0, fx_1, fy_0, fy_1, co, si;

for(k = 0; k<n; k++)

{

p_x = x; fy_0 = 0; fy_1 = 0; for(i=0; i<n; i++)

{

fx_0 = (double)p_x[0]; fx_1 = (double)p_x[1]; p_x += 2;

index = (i*k) % n; arg = 2*PI*index/n; co = cos(arg);

si = −sin(arg);

fy_0 += ((fx_0 * co) − (fx_1 * si)); fy_1 += ((fx_1 * co) + (fx_0 * si));

}

y[2*k] = (short)2*fy_0/sqrt(n); y[2*k+1] = (short)2*fy_1/sqrt(n);

}

}

Scaling by 2 (i.e., >>1) takes place at each

C64x+ DSPLIB Reference |