DSP_fft16x16r

Implementation Notes

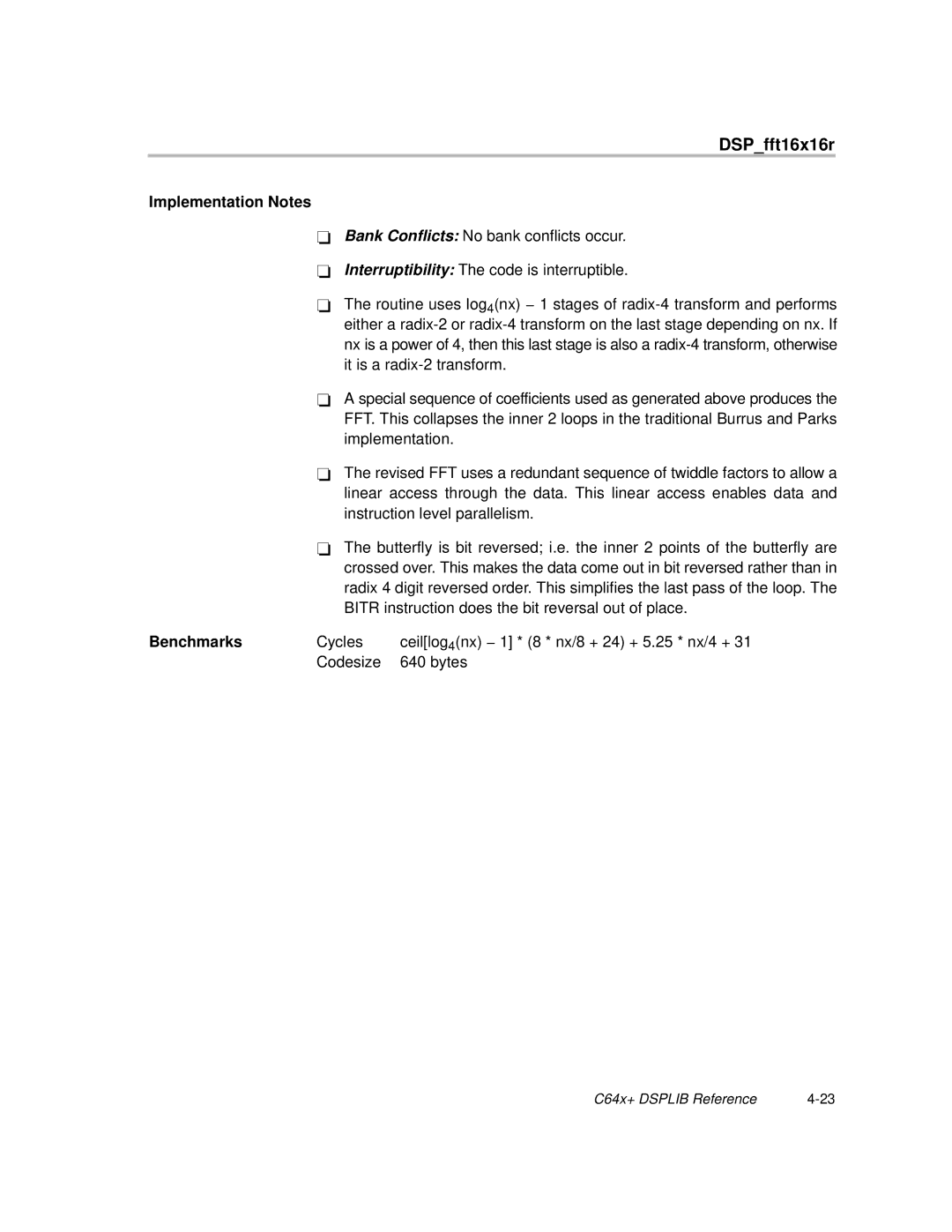

| - Bank Conflicts: No bank conflicts occur. | |

| - Interruptibility: The code is interruptible. | |

| - The routine uses log4(nx) − 1 stages of | |

| either a | |

| nx is a power of 4, then this last stage is also a | |

| it is a | |

| - A special sequence of coefficients used as generated above produces the | |

| FFT. This collapses the inner 2 loops in the traditional Burrus and Parks | |

| implementation. | |

| - The revised FFT uses a redundant sequence of twiddle factors to allow a | |

| linear access through the data. This linear access enables data and | |

| instruction level parallelism. | |

| - The butterfly is bit reversed; i.e. the inner 2 points of the butterfly are | |

| crossed over. This makes the data come out in bit reversed rather than in | |

| radix 4 digit reversed order. This simplifies the last pass of the loop. The | |

| BITR instruction does the bit reversal out of place. | |

Benchmarks | Cycles | ceil[log4(nx) − 1] * (8 * nx/8 + 24) + 5.25 * nx/4 + 31 |

| Codesize | 640 bytes |

C64x+ DSPLIB Reference |