Registers | www.ti.com |

3.4HC Interrupt and Status Register (HCINTERRUPTSTATUS)

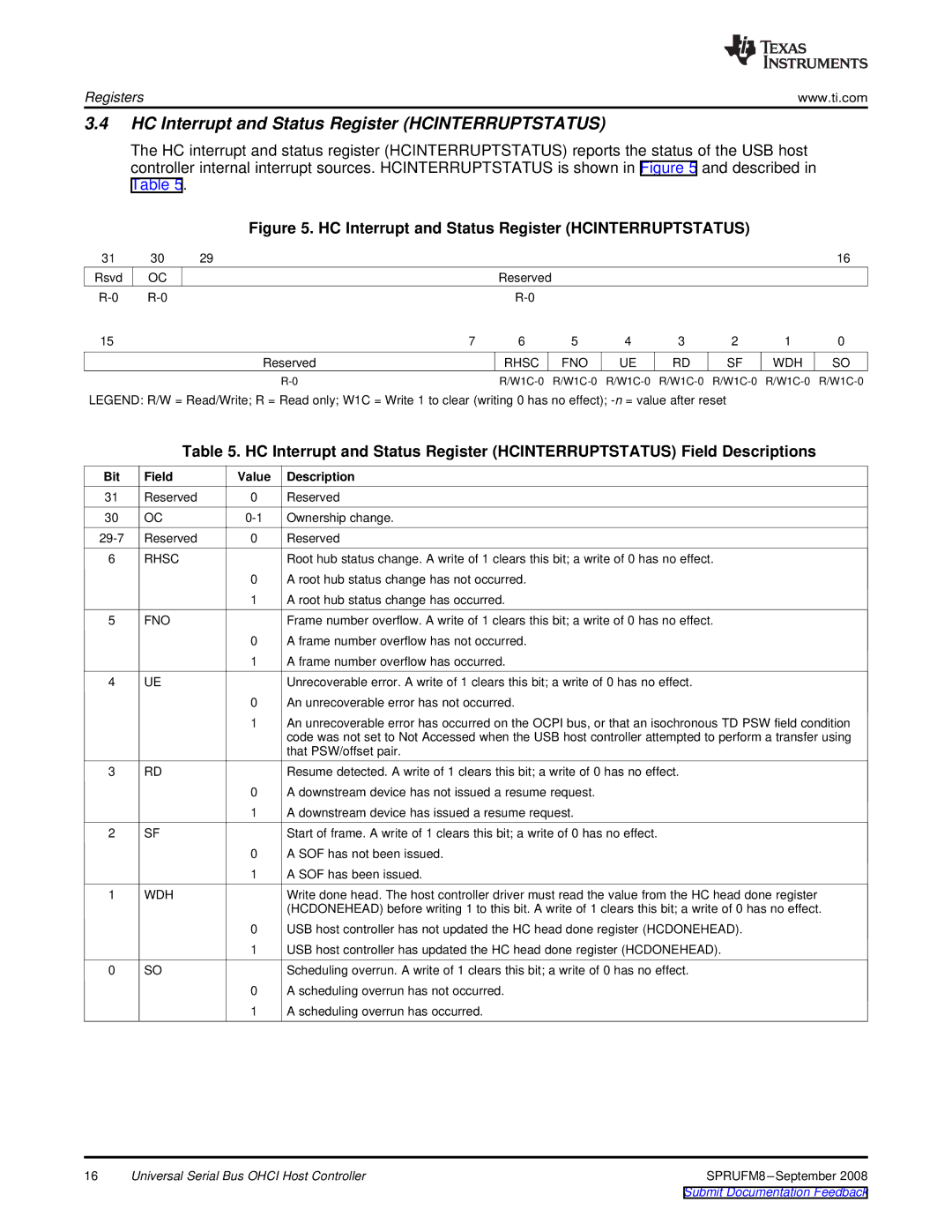

The HC interrupt and status register (HCINTERRUPTSTATUS) reports the status of the USB host controller internal interrupt sources. HCINTERRUPTSTATUS is shown in Figure 5 and described in Table 5.

Figure 5. HC Interrupt and Status Register (HCINTERRUPTSTATUS)

31 | 30 | 29 |

|

|

|

|

|

|

| 16 |

Rsvd | OC |

|

| Reserved |

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

15 |

|

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|

| Reserved |

| RHSC | FNO | UE | RD | SF | WDH | SO |

|

|

| ||||||||

LEGEND: R/W = Read/Write; R = Read only; W1C = Write 1 to clear (writing 0 has no effect); |

|

|

| |||||||

Table 5. HC Interrupt and Status Register (HCINTERRUPTSTATUS) Field Descriptions

Bit | Field | Value | Description |

31 | Reserved | 0 | Reserved |

30 | OC | Ownership change. | |

Reserved | 0 | Reserved | |

6 | RHSC |

| Root hub status change. A write of 1 clears this bit; a write of 0 has no effect. |

|

| 0 | A root hub status change has not occurred. |

|

| 1 | A root hub status change has occurred. |

5 | FNO |

| Frame number overflow. A write of 1 clears this bit; a write of 0 has no effect. |

|

| 0 | A frame number overflow has not occurred. |

|

| 1 | A frame number overflow has occurred. |

4 | UE |

| Unrecoverable error. A write of 1 clears this bit; a write of 0 has no effect. |

|

| 0 | An unrecoverable error has not occurred. |

1An unrecoverable error has occurred on the OCPI bus, or that an isochronous TD PSW field condition code was not set to Not Accessed when the USB host controller attempted to perform a transfer using that PSW/offset pair.

3 | RD | Resume detected. A write of 1 clears this bit; a write of 0 has no effect. |

| 0 | A downstream device has not issued a resume request. |

| 1 | A downstream device has issued a resume request. |

2 | SF | Start of frame. A write of 1 clears this bit; a write of 0 has no effect. |

| 0 | A SOF has not been issued. |

| 1 | A SOF has been issued. |

1 | WDH | Write done head. The host controller driver must read the value from the HC head done register |

|

| (HCDONEHEAD) before writing 1 to this bit. A write of 1 clears this bit; a write of 0 has no effect. |

| 0 | USB host controller has not updated the HC head done register (HCDONEHEAD). |

| 1 | USB host controller has updated the HC head done register (HCDONEHEAD). |

0 | SO | Scheduling overrun. A write of 1 clears this bit; a write of 0 has no effect. |

| 0 | A scheduling overrun has not occurred. |

| 1 | A scheduling overrun has occurred. |

16 | Universal Serial Bus OHCI Host Controller |

|

|

| Submit Documentation Feedback |