Registers | www.ti.com |

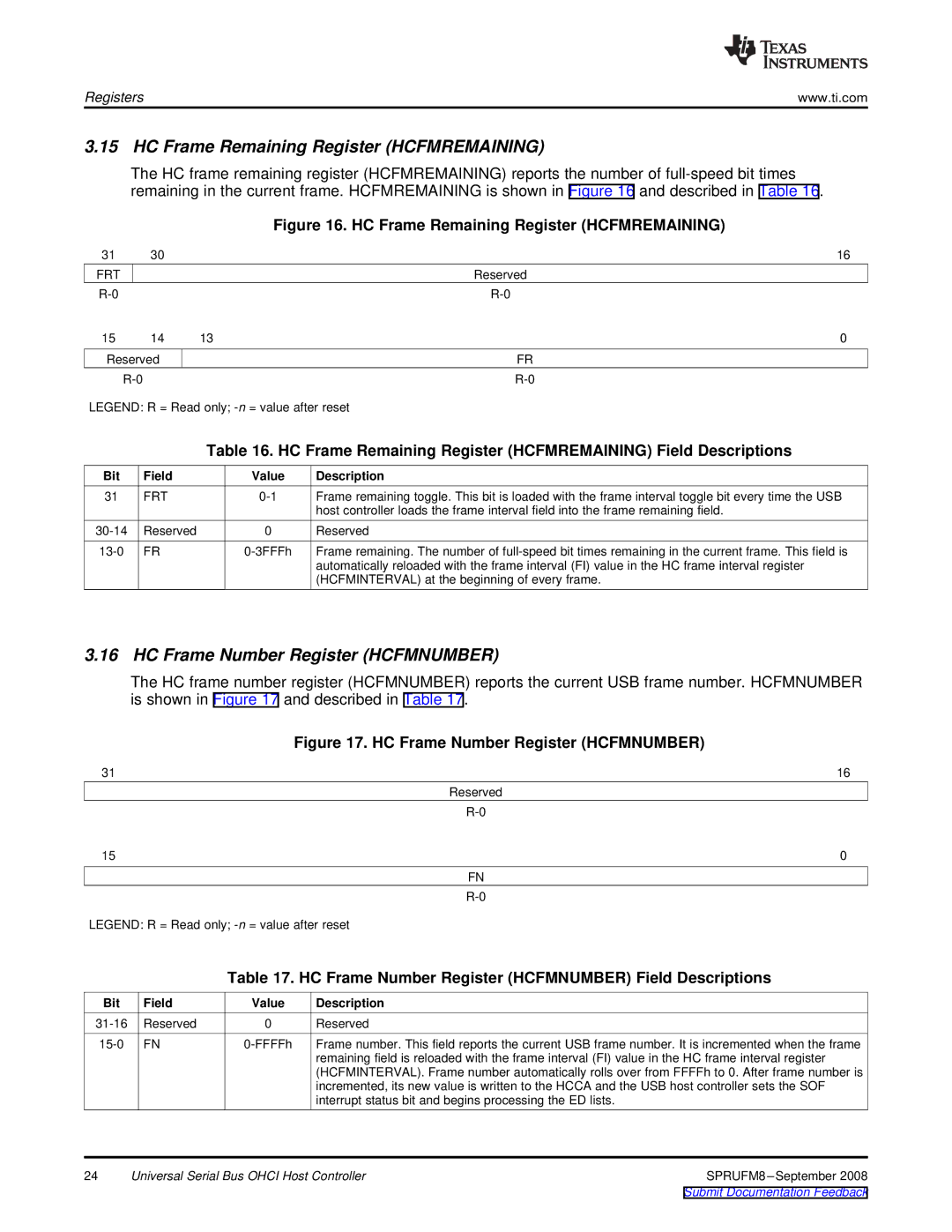

3.15 HC Frame Remaining Register (HCFMREMAINING)

The HC frame remaining register (HCFMREMAINING) reports the number of

|

| Figure 16. HC Frame Remaining Register (HCFMREMAINING) | |

31 | 30 |

| 16 |

FRT |

|

| Reserved |

|

| ||

15 | 14 | 13 | 0 |

Reserved |

| FR | |

|

| ||

LEGEND: R = Read only; | |||

|

| Table 16. HC Frame Remaining Register (HCFMREMAINING) Field Descriptions | |

Bit | Field | Value | Description |

31 | FRT | Frame remaining toggle. This bit is loaded with the frame interval toggle bit every time the USB | |

|

|

| host controller loads the frame interval field into the frame remaining field. |

Reserved | 0 | Reserved | |

FR | Frame remaining. The number of | ||

|

|

| automatically reloaded with the frame interval (FI) value in the HC frame interval register |

|

|

| (HCFMINTERVAL) at the beginning of every frame. |

3.16 HC Frame Number Register (HCFMNUMBER)

The HC frame number register (HCFMNUMBER) reports the current USB frame number. HCFMNUMBER is shown in Figure 17 and described in Table 17.

| Figure 17. HC Frame Number Register (HCFMNUMBER) |

31 | 16 |

| Reserved |

| |

15 | 0 |

| FN |

|

LEGEND: R = Read only;

Table 17. HC Frame Number Register (HCFMNUMBER) Field Descriptions

Bit | Field | Value | Description |

Reserved | 0 | Reserved | |

| FN |

| Frame number. This field reports the current USB frame number. It is incremented when the frame |

|

|

| remaining field is reloaded with the frame interval (FI) value in the HC frame interval register |

|

|

| (HCFMINTERVAL). Frame number automatically rolls over from FFFFh to 0. After frame number is |

|

|

| incremented, its new value is written to the HCCA and the USB host controller sets the SOF |

|

|

| interrupt status bit and begins processing the ED lists. |

24 | Universal Serial Bus OHCI Host Controller |

|

Submit Documentation Feedback