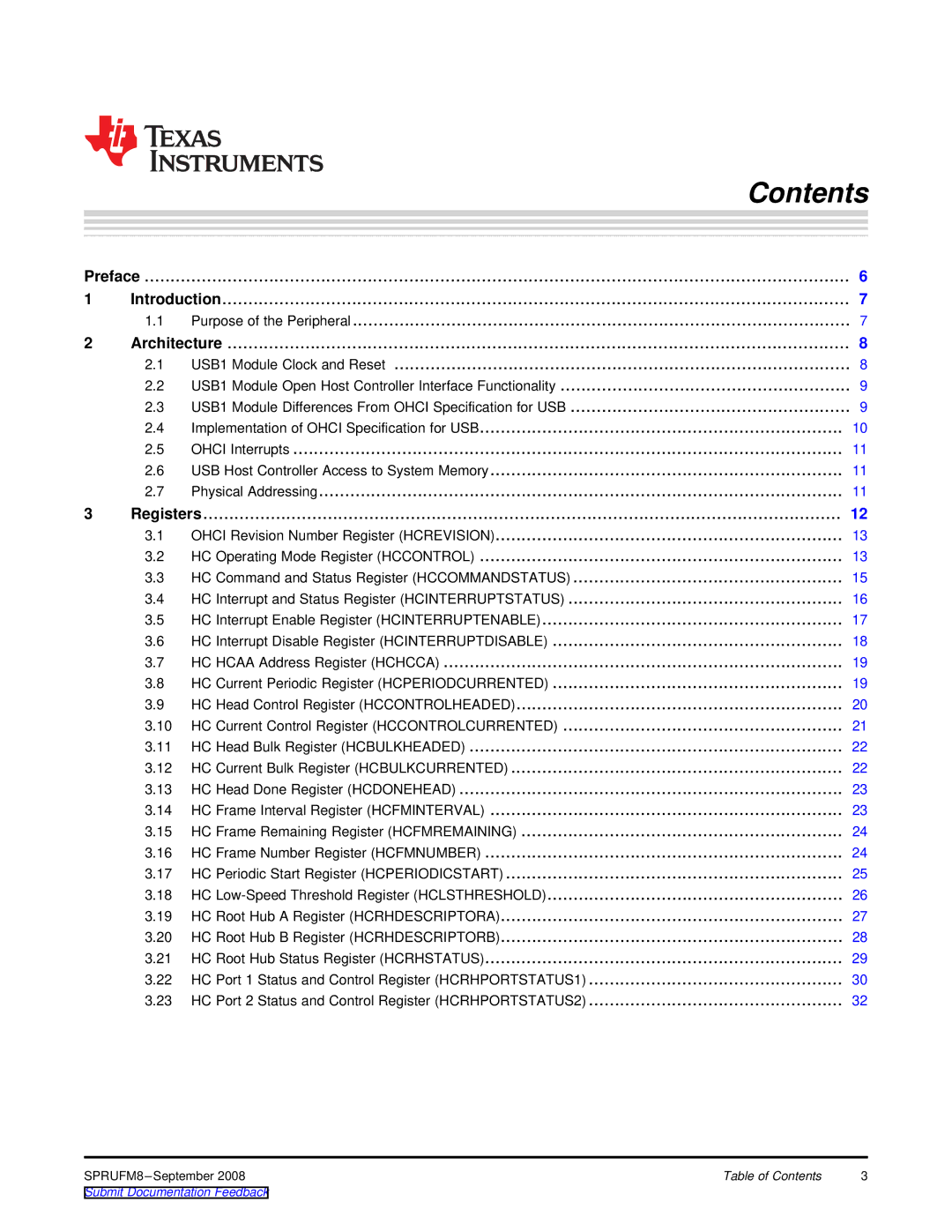

Contents

Preface | 6 | ||

1 | Introduction | 7 | |

| 1.1 | Purpose of the Peripheral | 7 |

2 | Architecture | 8 | |

| 2.1 | USB1 Module Clock and Reset | 8 |

| 2.2 | USB1 Module Open Host Controller Interface Functionality | 9 |

| 2.3 | USB1 Module Differences From OHCI Specification for USB | 9 |

| 2.4 | Implementation of OHCI Specification for USB | 10 |

| 2.5 | OHCI Interrupts | 11 |

| 2.6 | USB Host Controller Access to System Memory | 11 |

| 2.7 | Physical Addressing | 11 |

3 | Registers | 12 | |

| 3.1 | OHCI Revision Number Register (HCREVISION) | 13 |

| 3.2 | HC Operating Mode Register (HCCONTROL) | 13 |

| 3.3 | HC Command and Status Register (HCCOMMANDSTATUS) | 15 |

| 3.4 | HC Interrupt and Status Register (HCINTERRUPTSTATUS) | 16 |

| 3.5 | HC Interrupt Enable Register (HCINTERRUPTENABLE) | 17 |

| 3.6 | HC Interrupt Disable Register (HCINTERRUPTDISABLE) | 18 |

| 3.7 | HC HCAA Address Register (HCHCCA) | 19 |

| 3.8 | HC Current Periodic Register (HCPERIODCURRENTED) | 19 |

| 3.9 | HC Head Control Register (HCCONTROLHEADED) | 20 |

| 3.10 | HC Current Control Register (HCCONTROLCURRENTED) | 21 |

| 3.11 | HC Head Bulk Register (HCBULKHEADED) | 22 |

| 3.12 | HC Current Bulk Register (HCBULKCURRENTED) | 22 |

| 3.13 | HC Head Done Register (HCDONEHEAD) | 23 |

| 3.14 | HC Frame Interval Register (HCFMINTERVAL) | 23 |

| 3.15 | HC Frame Remaining Register (HCFMREMAINING) | 24 |

| 3.16 | HC Frame Number Register (HCFMNUMBER) | 24 |

| 3.17 | HC Periodic Start Register (HCPERIODICSTART) | 25 |

| 3.18 | HC | 26 |

| 3.19 | HC Root Hub A Register (HCRHDESCRIPTORA) | 27 |

| 3.20 | HC Root Hub B Register (HCRHDESCRIPTORB) | 28 |

| 3.21 | HC Root Hub Status Register (HCRHSTATUS) | 29 |

| 3.22 | HC Port 1 Status and Control Register (HCRHPORTSTATUS1) | 30 |

| 3.23 | HC Port 2 Status and Control Register (HCRHPORTSTATUS2) | 32 |

| Table of Contents | 3 |

Submit Documentation Feedback