www.ti.com | Registers |

3.5HC Interrupt Enable Register (HCINTERRUPTENABLE)

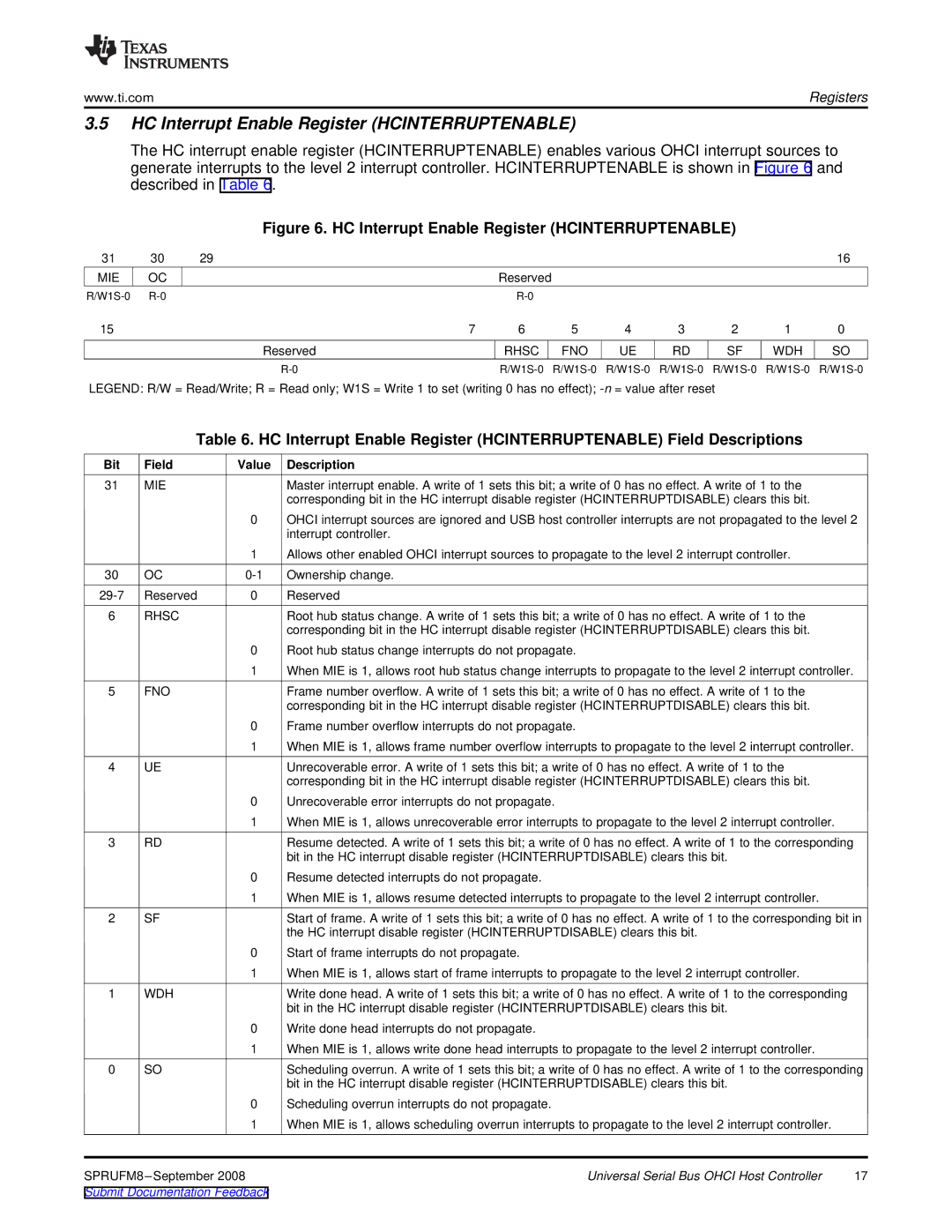

The HC interrupt enable register (HCINTERRUPTENABLE) enables various OHCI interrupt sources to generate interrupts to the level 2 interrupt controller. HCINTERRUPTENABLE is shown in Figure 6 and described in Table 6.

Figure 6. HC Interrupt Enable Register (HCINTERRUPTENABLE)

31 | 30 | 29 |

|

|

|

|

|

|

| 16 |

MIE | OC |

|

| Reserved |

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

15 |

|

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|

| Reserved |

| RHSC | FNO | UE | RD | SF | WDH | SO |

|

|

| ||||||||

LEGEND: R/W = Read/Write; R = Read only; W1S = Write 1 to set (writing 0 has no effect); |

|

|

| |||||||

|

| Table 6. HC Interrupt Enable Register (HCINTERRUPTENABLE) Field Descriptions |

Bit | Field | Value Description |

31 | MIE | Master interrupt enable. A write of 1 sets this bit; a write of 0 has no effect. A write of 1 to the |

|

| corresponding bit in the HC interrupt disable register (HCINTERRUPTDISABLE) clears this bit. |

0OHCI interrupt sources are ignored and USB host controller interrupts are not propagated to the level 2 interrupt controller.

|

| 1 | Allows other enabled OHCI interrupt sources to propagate to the level 2 interrupt controller. |

|

30 | OC | Ownership change. |

| |

Reserved | 0 | Reserved |

| |

6 | RHSC |

| Root hub status change. A write of 1 sets this bit; a write of 0 has no effect. A write of 1 to the |

|

|

|

| corresponding bit in the HC interrupt disable register (HCINTERRUPTDISABLE) clears this bit. |

|

|

| 0 | Root hub status change interrupts do not propagate. |

|

|

| 1 | When MIE is 1, allows root hub status change interrupts to propagate to the level 2 interrupt controller. |

|

5 | FNO |

| Frame number overflow. A write of 1 sets this bit; a write of 0 has no effect. A write of 1 to the |

|

|

|

| corresponding bit in the HC interrupt disable register (HCINTERRUPTDISABLE) clears this bit. |

|

|

| 0 | Frame number overflow interrupts do not propagate. |

|

|

| 1 | When MIE is 1, allows frame number overflow interrupts to propagate to the level 2 interrupt controller. |

|

4 | UE |

| Unrecoverable error. A write of 1 sets this bit; a write of 0 has no effect. A write of 1 to the |

|

|

|

| corresponding bit in the HC interrupt disable register (HCINTERRUPTDISABLE) clears this bit. |

|

|

| 0 | Unrecoverable error interrupts do not propagate. |

|

|

| 1 | When MIE is 1, allows unrecoverable error interrupts to propagate to the level 2 interrupt controller. |

|

3 | RD |

| Resume detected. A write of 1 sets this bit; a write of 0 has no effect. A write of 1 to the corresponding |

|

|

|

| bit in the HC interrupt disable register (HCINTERRUPTDISABLE) clears this bit. |

|

|

| 0 | Resume detected interrupts do not propagate. |

|

|

| 1 | When MIE is 1, allows resume detected interrupts to propagate to the level 2 interrupt controller. |

|

2 | SF |

| Start of frame. A write of 1 sets this bit; a write of 0 has no effect. A write of 1 to the corresponding bit in | |

|

|

| the HC interrupt disable register (HCINTERRUPTDISABLE) clears this bit. |

|

|

| 0 | Start of frame interrupts do not propagate. |

|

|

| 1 | When MIE is 1, allows start of frame interrupts to propagate to the level 2 interrupt controller. |

|

1 | WDH |

| Write done head. A write of 1 sets this bit; a write of 0 has no effect. A write of 1 to the corresponding |

|

|

|

| bit in the HC interrupt disable register (HCINTERRUPTDISABLE) clears this bit. |

|

|

| 0 | Write done head interrupts do not propagate. |

|

|

| 1 | When MIE is 1, allows write done head interrupts to propagate to the level 2 interrupt controller. |

|

0 | SO |

| Scheduling overrun. A write of 1 sets this bit; a write of 0 has no effect. A write of 1 to the corresponding | |

|

|

| bit in the HC interrupt disable register (HCINTERRUPTDISABLE) clears this bit. |

|

|

| 0 | Scheduling overrun interrupts do not propagate. |

|

|

| 1 | When MIE is 1, allows scheduling overrun interrupts to propagate to the level 2 interrupt controller. |

|

| Universal Serial Bus OHCI Host Controller | 17 | ||

Submit Documentation Feedback |

|

| ||