www.ti.comRegisters

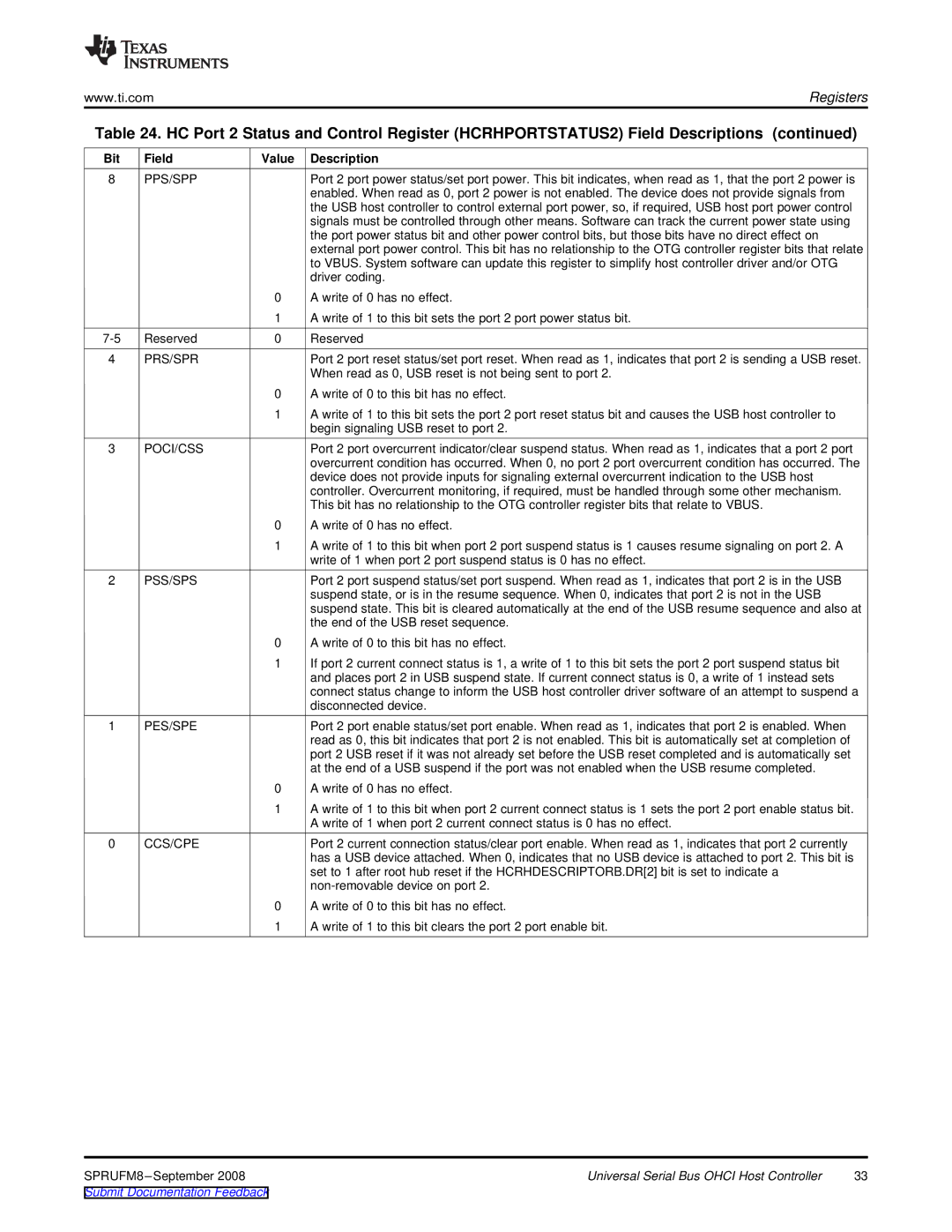

Table 24. HC Port 2 Status and Control Register (HCRHPORTSTATUS2) Field Descriptions (continued)

Bit | Field | Value | Description |

8 | PPS/SPP |

| Port 2 port power status/set port power. This bit indicates, when read as 1, that the port 2 power is |

|

|

| enabled. When read as 0, port 2 power is not enabled. The device does not provide signals from |

|

|

| the USB host controller to control external port power, so, if required, USB host port power control |

|

|

| signals must be controlled through other means. Software can track the current power state using |

|

|

| the port power status bit and other power control bits, but those bits have no direct effect on |

|

|

| external port power control. This bit has no relationship to the OTG controller register bits that relate |

|

|

| to VBUS. System software can update this register to simplify host controller driver and/or OTG |

|

|

| driver coding. |

|

| 0 | A write of 0 has no effect. |

|

| 1 | A write of 1 to this bit sets the port 2 port power status bit. |

Reserved | 0 | Reserved | |

4 | PRS/SPR |

| Port 2 port reset status/set port reset. When read as 1, indicates that port 2 is sending a USB reset. |

|

|

| When read as 0, USB reset is not being sent to port 2. |

|

| 0 | A write of 0 to this bit has no effect. |

|

| 1 | A write of 1 to this bit sets the port 2 port reset status bit and causes the USB host controller to |

|

|

| begin signaling USB reset to port 2. |

3 | POCI/CSS |

| Port 2 port overcurrent indicator/clear suspend status. When read as 1, indicates that a port 2 port |

|

|

| overcurrent condition has occurred. When 0, no port 2 port overcurrent condition has occurred. The |

|

|

| device does not provide inputs for signaling external overcurrent indication to the USB host |

|

|

| controller. Overcurrent monitoring, if required, must be handled through some other mechanism. |

|

|

| This bit has no relationship to the OTG controller register bits that relate to VBUS. |

|

| 0 | A write of 0 has no effect. |

|

| 1 | A write of 1 to this bit when port 2 port suspend status is 1 causes resume signaling on port 2. A |

|

|

| write of 1 when port 2 port suspend status is 0 has no effect. |

2 | PSS/SPS |

| Port 2 port suspend status/set port suspend. When read as 1, indicates that port 2 is in the USB |

|

|

| suspend state, or is in the resume sequence. When 0, indicates that port 2 is not in the USB |

|

|

| suspend state. This bit is cleared automatically at the end of the USB resume sequence and also at |

|

|

| the end of the USB reset sequence. |

|

| 0 | A write of 0 to this bit has no effect. |

|

| 1 | If port 2 current connect status is 1, a write of 1 to this bit sets the port 2 port suspend status bit |

|

|

| and places port 2 in USB suspend state. If current connect status is 0, a write of 1 instead sets |

|

|

| connect status change to inform the USB host controller driver software of an attempt to suspend a |

|

|

| disconnected device. |

1 | PES/SPE |

| Port 2 port enable status/set port enable. When read as 1, indicates that port 2 is enabled. When |

|

|

| read as 0, this bit indicates that port 2 is not enabled. This bit is automatically set at completion of |

|

|

| port 2 USB reset if it was not already set before the USB reset completed and is automatically set |

|

|

| at the end of a USB suspend if the port was not enabled when the USB resume completed. |

|

| 0 | A write of 0 has no effect. |

|

| 1 | A write of 1 to this bit when port 2 current connect status is 1 sets the port 2 port enable status bit. |

|

|

| A write of 1 when port 2 current connect status is 0 has no effect. |

0 | CCS/CPE |

| Port 2 current connection status/clear port enable. When read as 1, indicates that port 2 currently |

|

|

| has a USB device attached. When 0, indicates that no USB device is attached to port 2. This bit is |

|

|

| set to 1 after root hub reset if the HCRHDESCRIPTORB.DR[2] bit is set to indicate a |

|

|

|

|

|

| 0 | A write of 0 to this bit has no effect. |

|

| 1 | A write of 1 to this bit clears the port 2 port enable bit. |

| Universal Serial Bus OHCI Host Controller | 33 |

Submit Documentation Feedback |

|

|