www.ti.com | Architecture |

2.5OHCI Interrupts

The USB1 host controller can be controlled either by the ARM or the DSP. It has the ability to interrupt either processor.

2.6USB Host Controller Access to System Memory

The USB1 module needs to access system memory to read and write the OHCI data structures and data buffers associated with USB traffic. The switch fabric allows the USB host controller to access system memory, as shown in .

2.7Physical Addressing

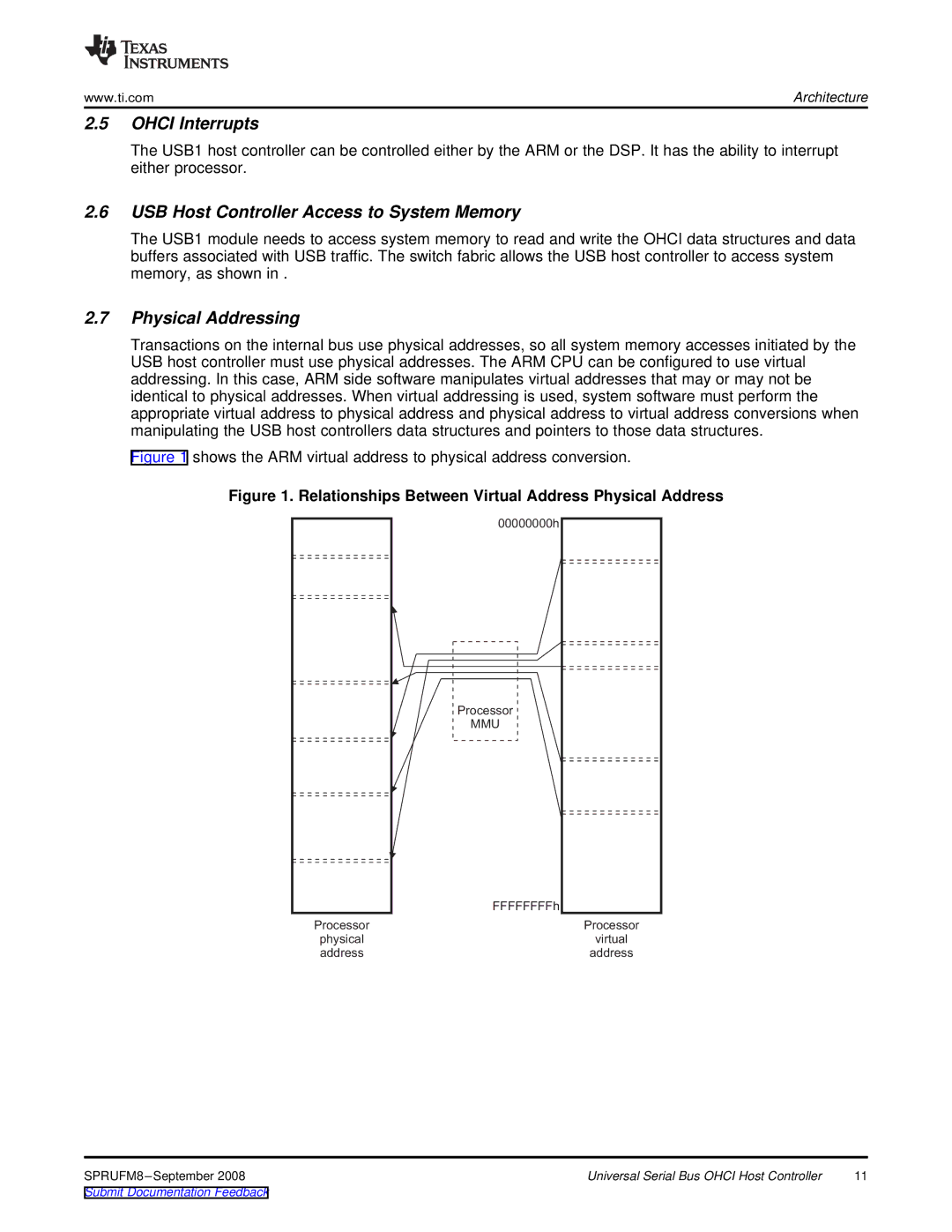

Transactions on the internal bus use physical addresses, so all system memory accesses initiated by the USB host controller must use physical addresses. The ARM CPU can be configured to use virtual addressing. In this case, ARM side software manipulates virtual addresses that may or may not be identical to physical addresses. When virtual addressing is used, system software must perform the appropriate virtual address to physical address and physical address to virtual address conversions when manipulating the USB host controllers data structures and pointers to those data structures.

Figure 1 shows the ARM virtual address to physical address conversion.

Figure 1. Relationships Between Virtual Address Physical Address

00000000h |

Processor |

MMU |

FFFFFFFFh |

Processor | Processor |

physical | virtual |

address | address |

| Universal Serial Bus OHCI Host Controller | 11 |

Submit Documentation Feedback