Power-On Self-Test (POST)

Each time you turn on the system, the

The

The main components on the main board that must be diagnosed and/or initialized by POST to ensure system functionality are as follows:

!Microprocessor with

!Direct Memory Access (DMA) controller

!Interrupt system

!Three programmable timers

!ROM subsystem

!RAM subsystem

!CMOS RAM subsystem and real time clock/calendar with battery backup

!Onboard parallel interface controller

!Embedded hard disk interface and one diskette drive interface

!Keyboard and auxiliary device controllers

!1.44M floppy controller

!I/O ports

!One parallel port

!One

!One

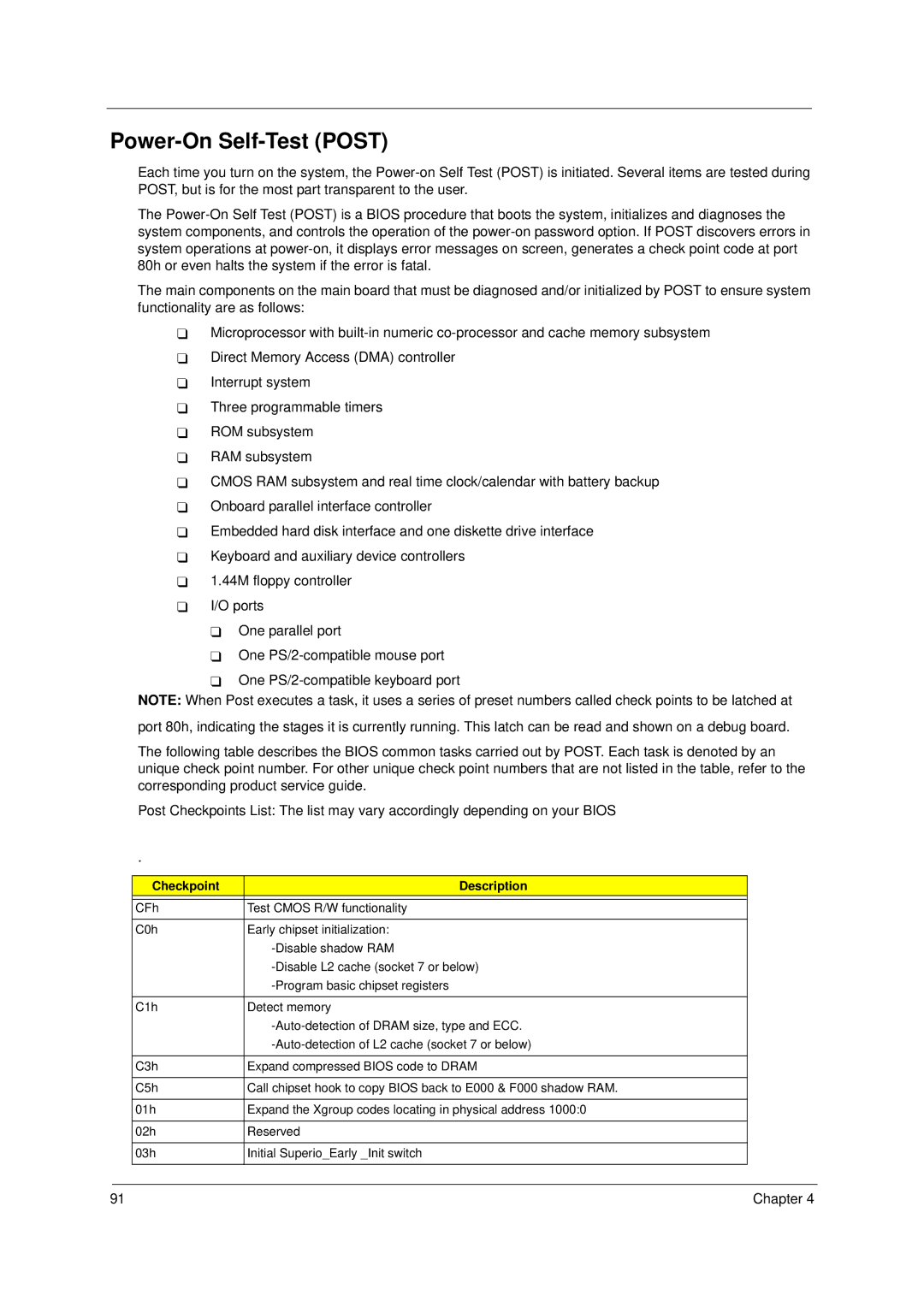

NOTE: When Post executes a task, it uses a series of preset numbers called check points to be latched at

port 80h, indicating the stages it is currently running. This latch can be read and shown on a debug board.

The following table describes the BIOS common tasks carried out by POST. Each task is denoted by an unique check point number. For other unique check point numbers that are not listed in the table, refer to the corresponding product service guide.

Post Checkpoints List: The list may vary accordingly depending on your BIOS

.

Checkpoint | Description |

|

|

CFh | Test CMOS R/W functionality |

|

|

C0h | Early chipset initialization: |

| |

| |

| |

|

|

C1h | Detect memory |

| |

| |

|

|

C3h | Expand compressed BIOS code to DRAM |

|

|

C5h | Call chipset hook to copy BIOS back to E000 & F000 shadow RAM. |

|

|

01h | Expand the Xgroup codes locating in physical address 1000:0 |

|

|

02h | Reserved |

|

|

03h | Initial Superio_Early _Init switch |

|

|

91 | Chapter 4 |