Chapter 3 | Hardware |

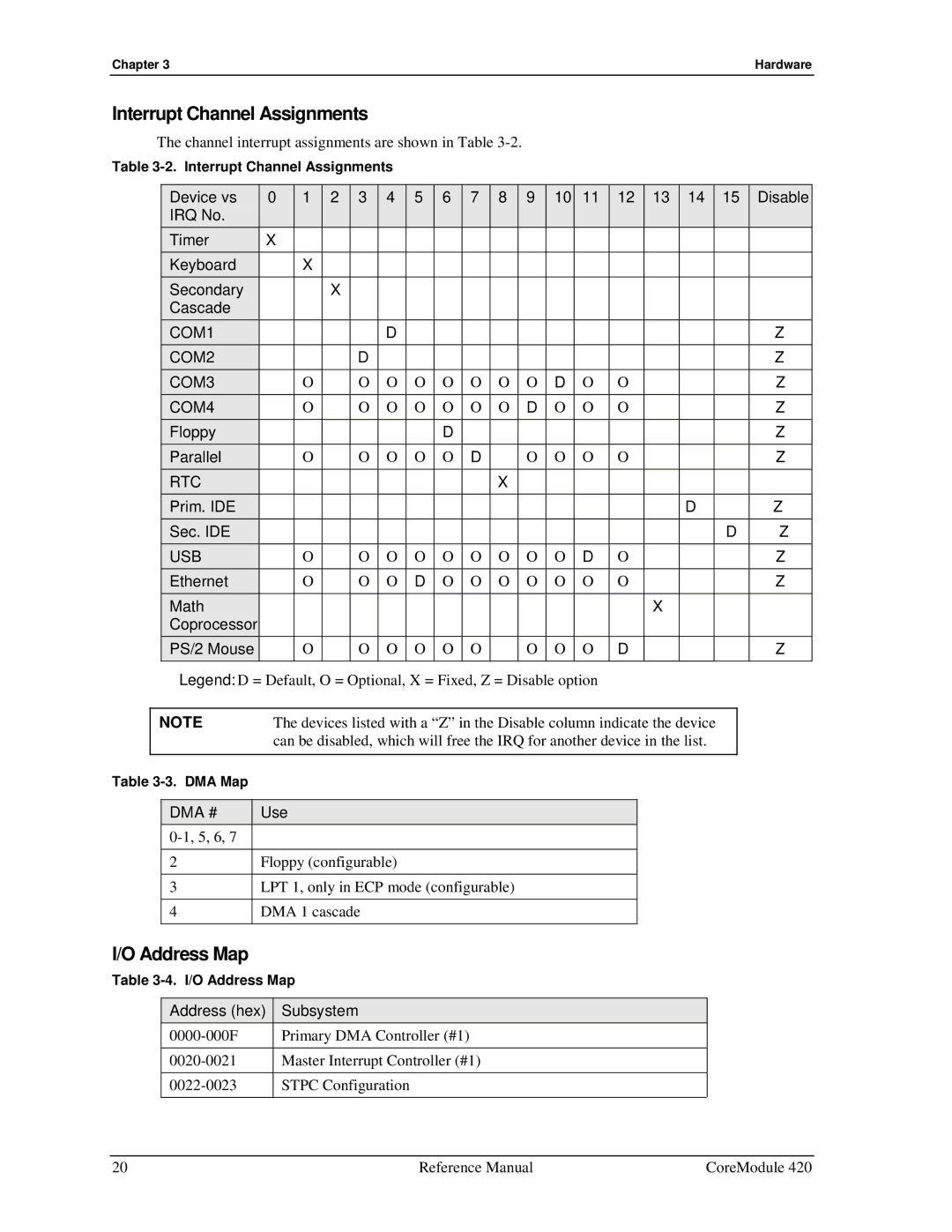

Interrupt Channel Assignments

The channel interrupt assignments are shown in Table

Table

|

| Device vs | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | Disable | |

|

| IRQ No. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Timer | X |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Keyboard |

| X |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Secondary |

|

| X |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Cascade |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| COM1 |

|

|

|

| D |

|

|

|

|

|

|

|

|

|

|

|

| Z |

|

| COM2 |

|

|

| D |

|

|

|

|

|

|

|

|

|

|

|

|

| Z |

|

| COM3 |

| O |

| O | O | O | O | O | O | O | D | O | O |

|

|

|

| Z |

|

| COM4 |

| O |

| O | O | O | O | O | O | D | O | O | O |

|

|

|

| Z |

|

| Floppy |

|

|

|

|

|

| D |

|

|

|

|

|

|

|

|

|

| Z |

|

| Parallel |

| O |

| O | O | O | O | D |

| O | O | O | O |

|

|

|

| Z |

|

| RTC |

|

|

|

|

|

|

|

| X |

|

|

|

|

|

|

|

|

|

|

| Prim. IDE |

|

|

|

|

|

|

|

|

|

|

|

|

|

| D |

|

| Z |

|

| Sec. IDE |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| D | Z | |

|

| USB |

| O |

| O | O | O | O | O | O | O | O | D | O |

|

|

|

| Z |

|

| Ethernet |

| O |

| O | O | D | O | O | O | O | O | O | O |

|

|

|

| Z |

|

| Math |

|

|

|

|

|

|

|

|

|

|

|

|

| X |

|

|

|

|

|

| Coprocessor |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| PS/2 Mouse |

| O |

| O | O | O | O | O |

| O | O | O | D |

|

|

|

| Z |

|

| Legend: D = Default, O = Optional, X = Fixed, Z = Disable option |

|

|

|

|

|

| ||||||||||||

|

|

|

|

| ||||||||||||||||

| NOTE | The devices listed with a “Z” in the Disable column indicate the device |

|

| ||||||||||||||||

|

|

| can be disabled, which will free the IRQ for another device in the list. |

|

| |||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

Table |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

DMA #

Use

2Floppy (configurable)

3LPT 1, only in ECP mode (configurable)

4DMA 1 cascade

I/O Address Map

Table

Address (hex) | Subsystem |

Primary DMA Controller (#1) | |

|

|

Master Interrupt Controller (#1) | |

|

|

STPC Configuration |

20 | Reference Manual | CoreModule 420 |