Chapter 3 | Hardware |

CPU (U14)

The CoreModule 420 uses an embedded microprocessor operating at 133MHz, that combines a powerful x86 core and a selection of peripheral interfaces into one chip. The STPC Atlas integrates a standard 5th generation x86 core. It supports logic including PC/104, UIDE controllers and combines these with standard I/O interfaces to provide a PC compatible subsystem in a single chip.

Memory

The CoreModule 420 memory consists of the following elements:

•SDRAM

•Flash memory

•Bytewide socket

SDRAM Memory (U7, U8, U9, U10)

The CoreModule 420 contains four

Flash Memory (U6)

A 1MB flash device is used for system BIOS on the module and 768kB is available for user code. The Flash memory also stores system parameters (CMOS settings) for

Bytewide Socket (U5)

The CoreModule 420 has a

A memory device installed in the bytewide socket can be used for:

•DOC2000

•External BIOS (BIOS recovery)

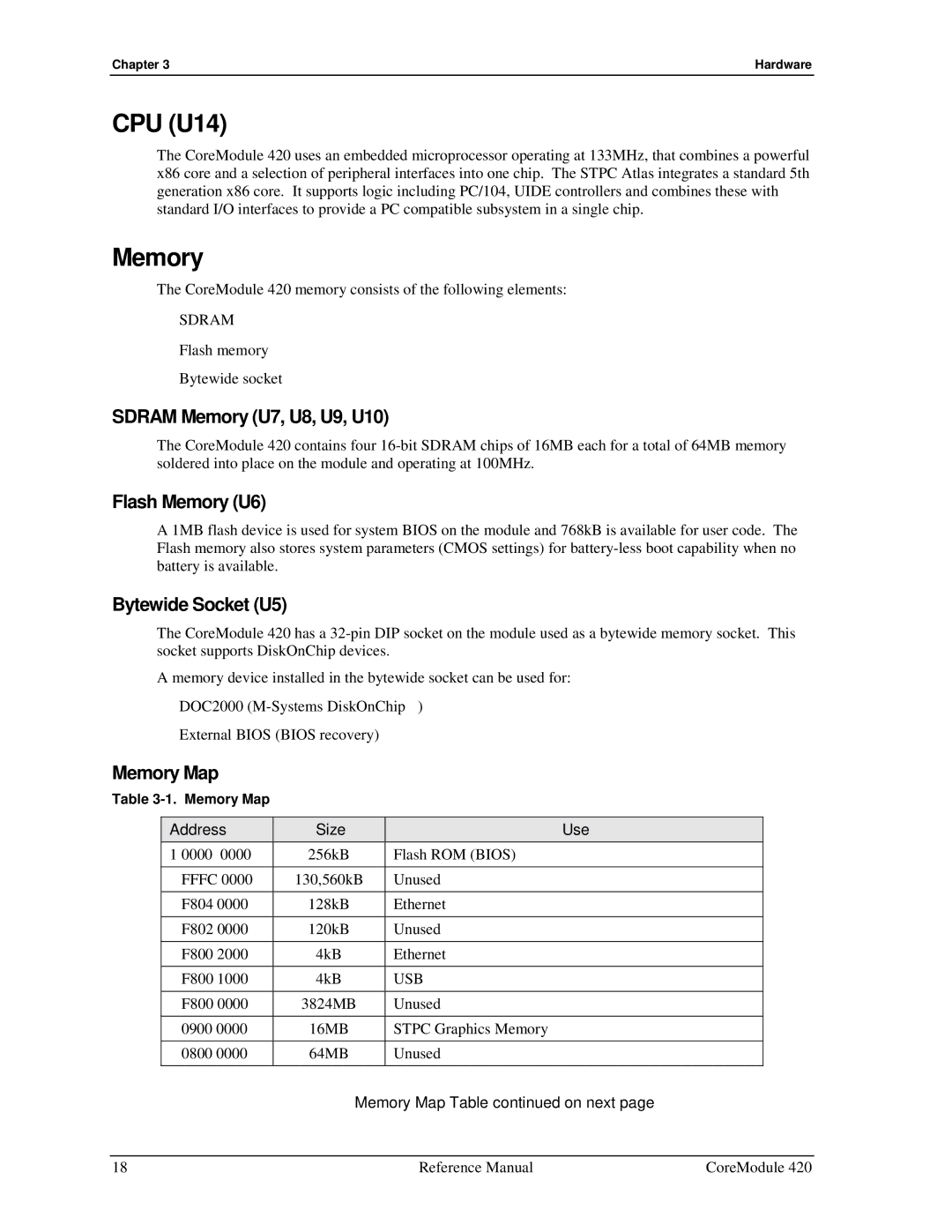

Memory Map

Table

Address | Size | Use |

1 0000 0000 | 256kB | Flash ROM (BIOS) |

|

|

|

FFFC 0000 | 130,560kB | Unused |

|

|

|

F804 0000 | 128kB | Ethernet |

|

|

|

F802 0000 | 120kB | Unused |

|

|

|

F800 2000 | 4kB | Ethernet |

|

|

|

F800 1000 | 4kB | USB |

|

|

|

F800 0000 | 3824MB | Unused |

|

|

|

0900 0000 | 16MB | STPC Graphics Memory |

|

|

|

0800 0000 | 64MB | Unused |

|

|

|

Memory Map Table continued on next page

18 | Reference Manual | CoreModule 420 |