Ultra37000 CPLD Family

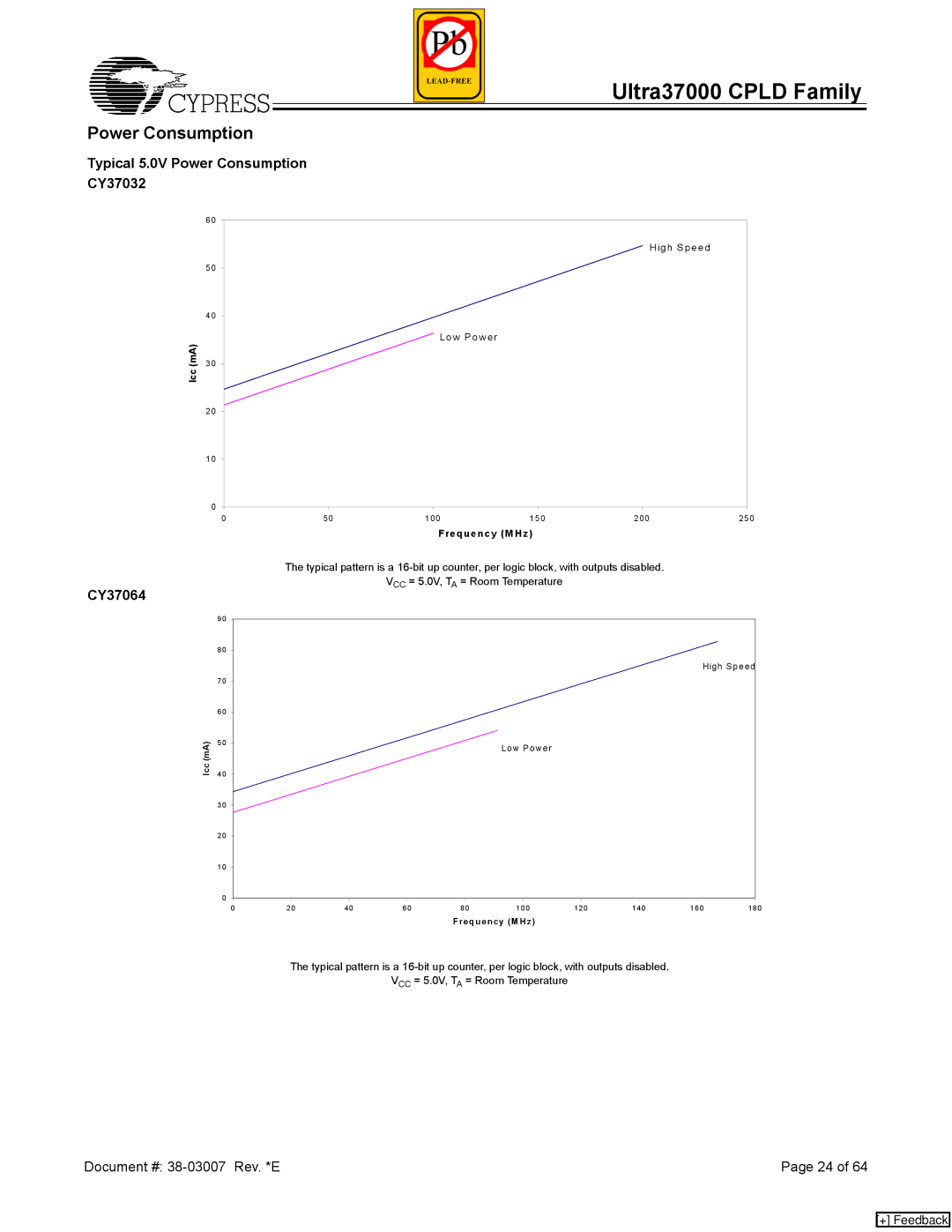

Power Consumption

Typical 5.0V Power Consumption

CY37032

| 6 0 |

|

|

|

|

|

|

|

|

|

|

| H igh S peed |

| 5 0 |

|

|

|

|

|

| 4 0 |

|

|

|

|

|

(mA) |

|

| Low P ow er |

|

|

|

3 0 |

|

|

|

|

| |

Icc |

|

|

|

|

|

|

| 2 0 |

|

|

|

|

|

| 1 0 |

|

|

|

|

|

| 0 |

|

|

|

|

|

| 0 | 5 0 | 1 0 0 | 1 5 0 | 2 0 0 | 2 5 0 |

Frequency (M H z)

The typical pattern is a

CY37064

VCC = 5.0V, TA = Room Temperature

| 9 0 |

|

|

|

|

|

|

|

|

|

| 8 0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| H igh S peed | |

| 7 0 |

|

|

|

|

|

|

|

|

|

| 6 0 |

|

|

|

|

|

|

|

|

|

Icc (mA) | 5 0 |

|

|

|

| Low P ower |

|

|

|

|

|

|

|

|

|

|

|

|

| ||

4 0 |

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

| |

| 3 0 |

|

|

|

|

|

|

|

|

|

| 2 0 |

|

|

|

|

|

|

|

|

|

| 1 0 |

|

|

|

|

|

|

|

|

|

| 0 |

|

|

|

|

|

|

|

|

|

| 0 | 2 0 | 40 | 6 0 | 8 0 | 1 0 0 | 12 0 | 1 40 | 1 6 0 | 18 0 |

Frequency (M Hz)

The typical pattern is a

VCC = 5.0V, TA = Room Temperature

Document #: | Page 24 of 64 |

[+] Feedback