Ultra37000 CPLD Family

FROM CLOCK POLARITY MUXES

INPUT PIN

|

|

|

|

| 0 |

|

|

|

|

|

| 1 | O |

|

|

|

|

| 2 | |

| D |

| D |

|

| |

0 | Q | Q | 3 |

| ||

1 | O |

|

|

| ||

|

|

|

|

| ||

2 |

|

|

|

| C12 C13 | |

|

|

|

|

| ||

3 |

|

|

|

|

| |

|

|

|

|

|

| |

C10 C11 |

|

|

|

|

|

|

| D | Q |

|

|

|

|

| LE |

|

|

|

|

|

Figure 3. Input Macrocell

TO PIM

FROM CLOCK POLARITY INPUT CLOCK PINS

|

|

|

|

|

| 0 | O |

| TO CLOCK MUX ON |

|

|

|

|

|

|

| 1 |

| ALL INPUT MACROCELLS | ||

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

| |

INPUT/CLOCK PIN |

|

|

|

|

| C12 |

|

|

| |

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

| 0 |

|

|

|

|

|

|

|

|

|

|

| O |

|

|

|

|

|

|

|

|

| 1 | TO CLOCK MUX |

|

|

|

|

|

|

|

|

|

| IN EACH |

|

|

|

|

|

|

|

|

|

| LOGIC BLOCK |

|

|

|

|

|

|

| 0 |

| C13, C14, C15 | OR C16 |

|

|

|

|

|

|

| 1 | O | TO PIM |

|

|

|

|

|

|

|

| 2 | CLOCK POLARITY MUX | ||

|

| D |

| D |

|

|

|

| ||

0 |

| Q | Q |

| 3 |

|

| ONE PER LOGIC BLOCK | ||

|

|

|

|

|

| |||||

1 | O |

|

|

|

|

|

|

|

| FOR EACH CLOCK INPUT |

2 |

|

|

|

|

| C10C11 |

|

|

| |

|

|

|

|

|

|

|

|

| ||

3 |

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

| |

| C8 C9 | D | Q |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

| LE |

|

|

|

|

|

|

|

|

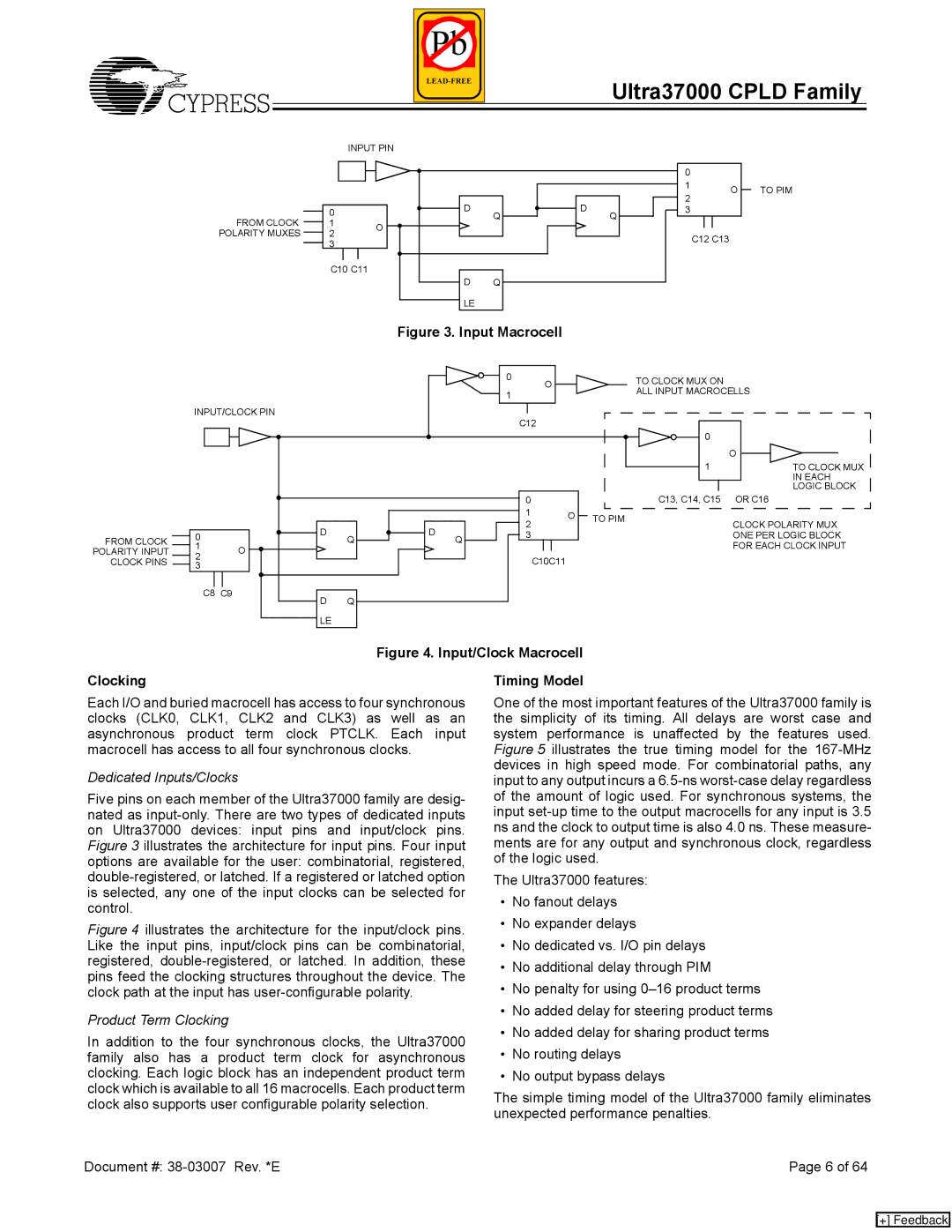

Figure 4. Input/Clock Macrocell

Clocking

Each I/O and buried macrocell has access to four synchronous clocks (CLK0, CLK1, CLK2 and CLK3) as well as an asynchronous product term clock PTCLK. Each input macrocell has access to all four synchronous clocks.

Dedicated Inputs/Clocks

Five pins on each member of the Ultra37000 family are desig- nated as

Figure 4 illustrates the architecture for the input/clock pins. Like the input pins, input/clock pins can be combinatorial, registered, double-registered, or latched. In addition, these pins feed the clocking structures throughout the device. The clock path at the input has user-configurable polarity.

Product Term Clocking

In addition to the four synchronous clocks, the Ultra37000 family also has a product term clock for asynchronous clocking. Each logic block has an independent product term clock which is available to all 16 macrocells. Each product term clock also supports user configurable polarity selection.

Timing Model

One of the most important features of the Ultra37000 family is the simplicity of its timing. All delays are worst case and system performance is unaffected by the features used. Figure 5 illustrates the true timing model for the

The Ultra37000 features:

•No fanout delays

•No expander delays

•No dedicated vs. I/O pin delays

•No additional delay through PIM

•No penalty for using

•No added delay for steering product terms

•No added delay for sharing product terms

•No routing delays

•No output bypass delays

The simple timing model of the Ultra37000 family eliminates unexpected performance penalties.

Document #: | Page 6 of 64 |

[+] Feedback