Ultra37000 CPLD Family

|

| COMBINATORIAL SIGNAL |

|

| |||

|

|

|

| ||||

|

|

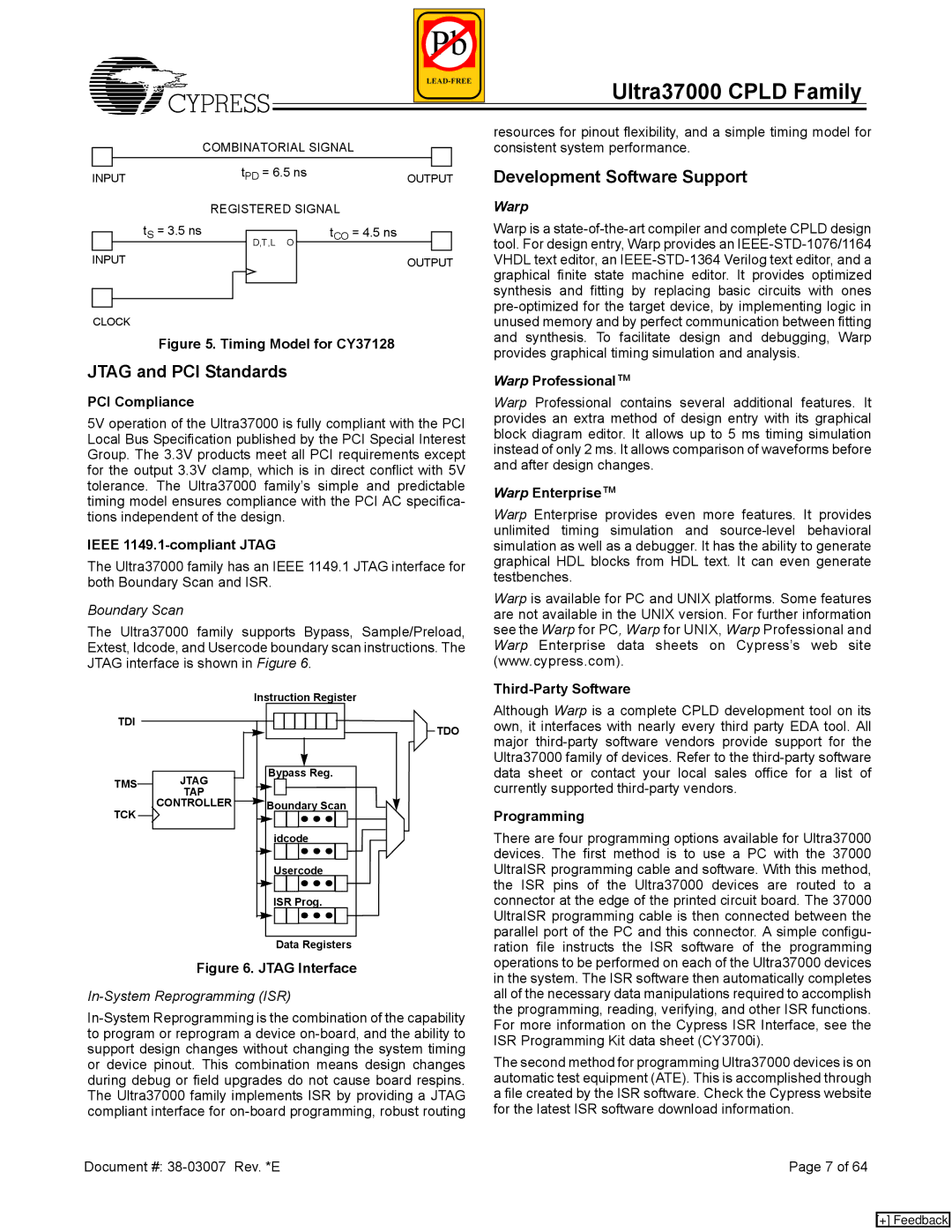

| tPD = 6.5 ns |

|

| ||

INPUT | OUTPUT | ||||||

|

| REGISTERED SIGNAL |

|

| |||

| tS = 3.5 ns |

|

|

| tCO = 4.5 ns |

|

|

|

|

| D,T,L O |

|

| ||

|

|

|

|

|

|

| |

INPUT |

|

|

|

| OUTPUT | ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CLOCK

Figure 5. Timing Model for CY37128

resources for pinout flexibility, and a simple timing model for consistent system performance.

Development Software Support

Warp

Warp is a

JTAG and PCI Standards

PCI Compliance

5V operation of the Ultra37000 is fully compliant with the PCI Local Bus Specification published by the PCI Special Interest Group. The 3.3V products meet all PCI requirements except for the output 3.3V clamp, which is in direct conflict with 5V tolerance. The Ultra37000 family’s simple and predictable timing model ensures compliance with the PCI AC specifica- tions independent of the design.

IEEE 1149.1-compliant JTAG

The Ultra37000 family has an IEEE 1149.1 JTAG interface for both Boundary Scan and ISR.

Boundary Scan

The Ultra37000 family supports Bypass, Sample/Preload, Extest, Idcode, and Usercode boundary scan instructions. The JTAG interface is shown in Figure 6.

Instruction Register

Warp Professional™

Warp Professional contains several additional features. It provides an extra method of design entry with its graphical block diagram editor. It allows up to 5 ms timing simulation instead of only 2 ms. It allows comparison of waveforms before and after design changes.

Warp Enterprise™

Warp Enterprise provides even more features. It provides unlimited timing simulation and

Warp is available for PC and UNIX platforms. Some features are not available in the UNIX version. For further information see the Warp for PC, Warp for UNIX, Warp Professional and Warp Enterprise data sheets on Cypress’s web site (www.cypress.com).

Third-Party Software

TDI

TMS

TCK

JTAG

TAP

CONTROLLER ![]()

Bypass Reg.

Boundary Scan

idcode |

Usercode |

TDO

Although Warp is a complete CPLD development tool on its own, it interfaces with nearly every third party EDA tool. All major

Programming

There are four programming options available for Ultra37000 devices. The first method is to use a PC with the 37000 UltraISR programming cable and software. With this method, the ISR pins of the Ultra37000 devices are routed to a

ISR Prog.

Data Registers

Figure 6. JTAG Interface

In-System Reprogramming (ISR)

connector at the edge of the printed circuit board. The 37000 UltraISR programming cable is then connected between the parallel port of the PC and this connector. A simple configu- ration file instructs the ISR software of the programming operations to be performed on each of the Ultra37000 devices in the system. The ISR software then automatically completes all of the necessary data manipulations required to accomplish the programming, reading, verifying, and other ISR functions. For more information on the Cypress ISR Interface, see the ISR Programming Kit data sheet (CY3700i).

The second method for programming Ultra37000 devices is on automatic test equipment (ATE). This is accomplished through a file created by the ISR software. Check the Cypress website for the latest ISR software download information.

Document #: | Page 7 of 64 |

[+] Feedback