CY7C1380D, CY7C1382D CY7C1380F, CY7C1382F

when the EXTEST is entered as the current instruction. When HIGH, it enables the output buffers to drive the output bus. When LOW, this bit places the output bus into a

This bit can be set by entering the SAMPLE/PRELOAD or EXTEST command, and then shifting the desired bit into that cell, during the

output

Reserved

These instructions are not implemented but are reserved for future use. Do not use these instructions.

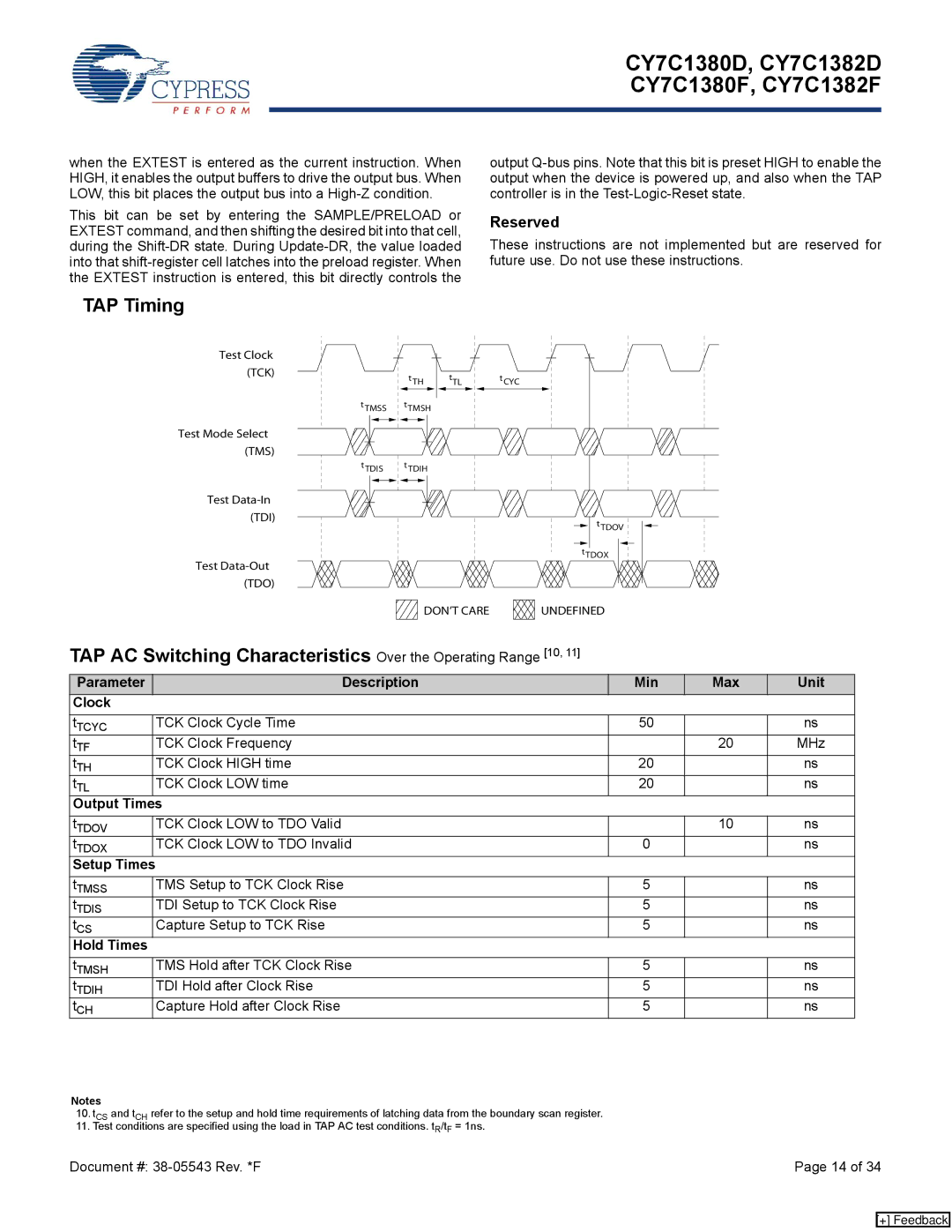

TAP Timing

Test Clock |

|

(TCK) | tTH |

| |

| tTMSS tTMSH |

Test Mode Select (TMS)

tTDIS tTDIH

Test

tTL tCYC

tTDOV

tTDOX

Test

DON’T CARE

![]() UNDEFINED

UNDEFINED

TAP AC Switching Characteristics Over the Operating Range [10, 11]

Parameter | Description | Min | Max | Unit |

Clock |

|

|

|

|

tTCYC | TCK Clock Cycle Time | 50 |

| ns |

tTF | TCK Clock Frequency |

| 20 | MHz |

tTH | TCK Clock HIGH time | 20 |

| ns |

tTL | TCK Clock LOW time | 20 |

| ns |

Output Times |

|

|

|

|

tTDOV | TCK Clock LOW to TDO Valid |

| 10 | ns |

tTDOX | TCK Clock LOW to TDO Invalid | 0 |

| ns |

Setup Times |

|

|

|

|

tTMSS | TMS Setup to TCK Clock Rise | 5 |

| ns |

tTDIS | TDI Setup to TCK Clock Rise | 5 |

| ns |

tCS | Capture Setup to TCK Rise | 5 |

| ns |

Hold Times |

|

|

|

|

tTMSH | TMS Hold after TCK Clock Rise | 5 |

| ns |

tTDIH | TDI Hold after Clock Rise | 5 |

| ns |

tCH | Capture Hold after Clock Rise | 5 |

| ns |

Notes

10.tCS and tCH refer to the setup and hold time requirements of latching data from the boundary scan register.

11.Test conditions are specified using the load in TAP AC test conditions. tR/tF = 1ns.

Document #: | Page 14 of 34 |

[+] Feedback