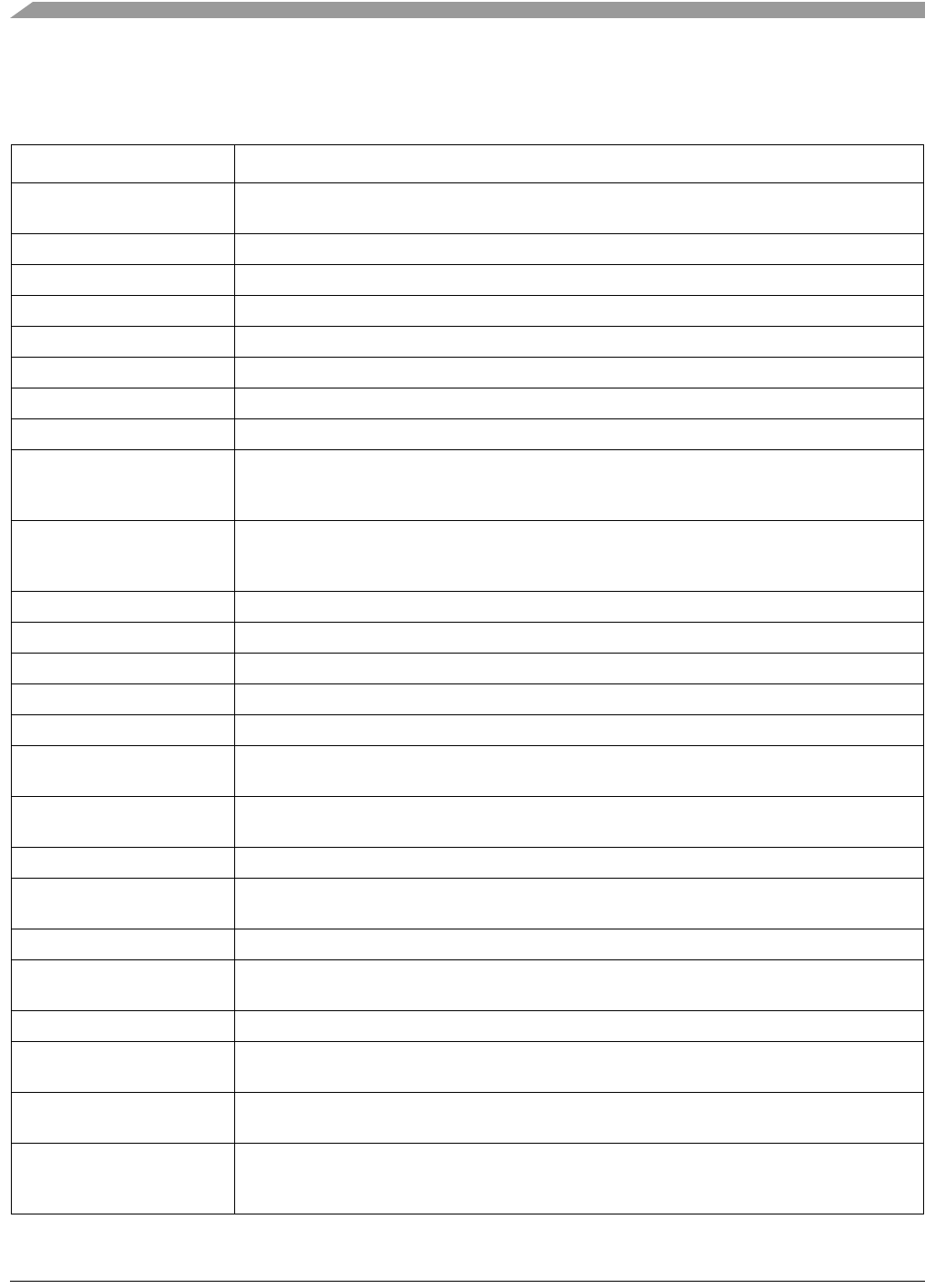

Main

How to Reach Us:

Chapter 1 Overview

Chapter 2 Signal Descriptions

Chapter 3 ColdFire Core

Chapter 4 Multiply-Accumulate Unit (MAC)

Chapter 5 Static RAM (SRAM)

Chapter 6 Clock Module

Chapter 7 Backup Watchdog Timer (BWT) Module

Chapter 8 Power Management

Chapter 9 Chip Configuration Module (CCM)

Chapter 10 Reset Controller Module

Chapter 11 Real-Time Clock

Chapter 12 System Control Module (SCM)

Chapter 13 General Purpose I/O Module

Chapter 14 Interrupt Controller Module

Chapter 15 Universal Serial Bus, OTG Capable Controller

Chapter 16 Edge Port Module (EPORT)

Chapter 17 DMA Controller Module

Chapter 18 ColdFire Flash Module (CFM)

Chapter 19 EzPort

Chapter 20 Programmable Interrupt Timers (PIT0PIT1)

Chapter 21 General Purpose Timer Module (GPT)

Chapter 22 DMA Timers (DTIM0DTIM3)

Chapter 23 Queued Serial Peripheral Interface (QSPI)

Chapter 24 UART Modules

Chapter 25 I2C Interface

Chapter 26 Analog-to-Digital Converter (ADC)

Chapter 27 Pulse-Width Modulation (PWM) Module

Chapter 28 Debug Module

Chapter 29 IEEE 1149.1 Test Access Port (JTAG)

Chapter 1 Overview

1.1 MCF52211 Family Configurations

1.2 Block Diagram

Figure 1-1. MCF52211 Block Diagram

1.3 Part Numbers and Packaging

V2 ColdFire CPU

1.2 Features

Page

Page

Page

1.2.1 V2 Core Overview

1.2.2 Integrated Debug Module

1.2.3 JTAG

1.2.4 On-Chip Memories

1.2.4.1 SRAM

1.2.4.2 Flash Memory

1.2.5 Power Management

1.2.6 USB On-The-Go Controller

1.2.7 UARTs

1.2.8 I2C Bus

1.2.9 QSPI

1.2.10 Fast ADC

1.2.11 DMA Timers (DTIM0DTIM3)

1.2.12 General Purpose Timer (GPT)

1.2.13 Periodic Interrupt Timers (PIT0 and PIT1)

1.2.14 Real-Time Clock (RTC)

1.2.15 Pulse-Width Modulation (PWM) Timers

1.2.16 Software Watchdog Timer

1.2.17 Backup Watchdog Timer

1.2.18 Phase-Locked Loop (PLL)

1.2.19 Interrupt Controller (INTC)

1.2.20 DMA Controller

1.2.21 Reset

Page

Chapter 2 Signal Descriptions

2.1 Introduction

2.2 Overview

Figure 2-1. Block Diagram with Signal Interfaces

2.3 Pin Functions

V2 ColdFire CPU

Table 2-1. Pin Functions by Primary and Alternate Purpose

Page

Page

Page

Page

2.4 Reset Signals

Table 2-2 describes signals that are used to reset the chip or as a reset indication.

Table 2-4 describes signals used in mode selection, Table 2-5 describes particular clocking modes.

2.5 PLL and Clock Signals

Table 2-3 describes signals that are used to support the on-chip clock generation circuitry.

2.7 External Interrupt Signals

Table 2-6 describes the external interrupt signals.

Table 2-7 describes the QSPI signals.

2.8 Queued Serial Peripheral Interface (QSPI)

Table 2-5. Clocking Modes

2.9 I2C I/O Signals

Table 2-8 describes the I2C serial interface module signals.

Table 2-10 describes the signals of the four DMA timer modules.

2.10 UART Module Signals

Table 2-9 describes the UART module signals.

2.12 ADC Signals

Table 2-11 describes the signals of the analog-to-digital converter.

2.13 General Purpose Timer Signals

Table 2-12 describes the general purpose timer signals.

2.14 Pulse-Width Modulator Signals

Table 2-14. Debug Support Signals (continued)

2.16 EzPort Signal Descriptions

Table 2-15 contains a list of EzPort external signals

2.17 Power and Ground Pins

Table 2-15. EzPort Signal Descriptions

Table 2-16. Power and Ground Pins

Page

Chapter 3 ColdFire Core

3.1 Introduction

3.1.1 Overview

Figure 3-1. V2 ColdFire Core Pipelines

3.2 Memory Map/Register Description

Table 3-1. ColdFire Core Programming Model

Two 32-bit memory base address registers (RAMBAR, FLASHBAR)

3.2.1 Data Registers (D0D7)

3.2.2 Address Registers (A0A6)

3.2.3 Supervisor/User Stack Pointers (A7 and OTHER_A7)

3.2.4 Condition Code Register (CCR)

3.2.5 Program Counter (PC)

Figure 3-6. Program Counter Register (PC)

3.2.6 Vector Base Register (VBR)

Figure 3-5. Condition Code Register (CCR) Table 3-2. CCR Field Descriptions

3.2.7 Status Register (SR)

3.3 Functional Description

3.3.1 Version 2 ColdFire Microarchitecture

3.2.8 Memory Base Address Registers (RAMBAR, FLASHBAR)

Page

Page

Figure 3-12. V2 OEP Embedded-Load Part 1

Figure 3-13. V2 OEP Embedded-Load Part 2

Page

3.3.2 Instruction Set Architecture (ISA_A+)

3.3.3 Exception Processing Overview

Page

3.3.3.1 Exception Stack Frame Definition

3.3.4 Processor Exceptions

3.3.4.1 Access Error Exception

3.3.4.2 Address Error Exception

3.3.4.3 Illegal Instruction Exception

3.3.4.4 Divide-By-Zero

3.3.4.5 Privilege Violation

3.3.4.6 Trace Exception

3.3.4.7 Unimplemented Line-A Opcode

3.3.4.8 Unimplemented Line-F Opcode

3.3.4.9 Debug Interrupt

3.3.4.10 RTE and Format Error Exception

3.3.4.11 TRAP Instruction Exception

3.3.4.12 Unsupported Instruction Exception

3.3.4.13 Interrupt Exception

3.3.4.14 Fault-on-Fault Halt

3.3.4.15 Reset Exception

Page

Figure 3-19. D1 Hardware Configuration Info

Table 3-9. D0 Hardware Configuration Info Field Description (continued)

Table 3-10. D1 Hardware Configuration Information Field Description

3.3.5 Instruction Execution Timing

3.3.5.1 Timing Assumptions

3.3.5.2 MOVE Instruction Execution Times

Table 3-12 lists execution times for MOVE.{B,W} instructions; Table 3-13 lists timings for MOVE.L.

Table 3-12. MOVE Byte and Word Execution Times

Table 3-13. MOVE Long Execution Times

3.3.5.3 Standard One Operand Instruction Execution Times

Table 3-14. One Operand Instruction Execution Times

Table 3-13. MOVE Long Execution Times (continued)

3.3.5.4 Standard Two Operand Instruction Execution Times

Table 3-15. Two Operand Instruction Execution Times

3.3.5.5 Miscellaneous Instruction Execution Times

Table 3-16. Miscellaneous Instruction Execution Times

Table 3-15. Two Operand Instruction Execution Times (continued)

3.3.5.6 MAC Instruction Execution Times

Table 3-17. MAC Instruction Execution Times

Table 3-16. Miscellaneous Instruction Execution Times (continued)

3.3.5.7 Branch Instruction Execution Times

Table 3-18. General Branch Instruction Execution Times

Table 3-19. Bcc Instruction Execution Times

Page

Chapter 4 Multiply-Accumulate Unit (MAC)

4.1 Introduction

4.1.1 Overview

4.1.1.1 Introduction to the MAC

4.2 Memory Map/Register Definition

Figure 4-2. MAC Status Register (MACSR) Table 4-2. MACSR Field Descriptions

4.2.2 Mask Register (MASK)

Figure 4-3. Mask Register (MASK)

Figure 4-4. Accumulator Register (ACC)

4.2.3 Accumulator Register (ACC)

Table 4-4. MASK Field Descriptions

4.3 Functional Description

4.3.1 Fractional Operation Mode

4.3.1.1 Rounding

4.3.1.2 Saving and Restoring the MAC Programming Model

4.3.1.3 MULS/MULU

4.3.1.4 Scale Factor in MAC or MSAC Instructions

4.3.2 MAC Instruction Set Summary

4.3.3 MAC Instruction Execution Times

4.3.4 Data Representation

4.3.5 MAC Opcodes

Page

Page

Page

Page

Page

Chapter 5 Static RAM (SRAM)

5.1 Introduction

5.1.1 Overview

5.1.2 Features

5.2 Memory Map/Register Description

5.2.1 SRAM Base Address Register (RAMBAR)

5.3 Initialization/Application Information

Table 5-2. RAMBAR Field Descriptions (continued)

5.3.1 SRAM Initialization Code

5.3.2 Power Management

Chapter 6 Clock Module

6.1 Introduction

6.2 Features

6.3 Modes of Operation

6.3.1 Backup Watchdog Timer Mode

6.4 Low-Power Mode Operation

6.5 Block Diagram

Figure 6-1. Clock Module Block Diagram

6.6 Signal Descriptions

6.6.1 EXTAL

6.6.2 XTAL

6.6.3 CLKOUT

6.6.4 CLKMOD[1:0]

6.7 Memory Map and Registers

6.7.1 Register Descriptions

Table 6-4. Clock Module Memory Map

6.7.1.1 Synthesizer Control Register (SYNCR)

Figure 6-2. Synthesizer Control Register (SYNCR) Table 6-5. SYNCR Field Descriptions

Table 6-5. SYNCR Field Descriptions (continued)

6.7.1.2 Synthesizer Status Register (SYNSR)

Figure 6-3. Synthesizer Status Register (SYNSR)

Table 6-5. SYNCR Field Descriptions (continued)

Table 6-6. SYNSR Field Descriptions

6.7.1.3 Relaxation Oscillator Control Register (ROCR)

6.7.1.4 Low-Power Divider Register (LPDR)

6.7.1.5 Clock Control High Register (CCHR)

6.7.1.6 Clock Control Low Register (CCLR)

6.7.1.7 Oscillator Control High Register (OCHR)

The OCHR is used to enable and configure the relaxation oscillator.

Figure 6-7. Clock Control Low Register (CCLR) Table 6-10. CCLR Field Descriptions

Table 6-11. CCLR[OSCSEL1] and CCLR[OSCSEL0] Settings

6.7.1.8 Oscillator Control Low Register (OCLR)

The OCLR is used to enable and configure the external oscillator.

Figure 6-9. Oscillator Control Low Register (OCLR)

Figure 6-8. Oscillator Control High Register (OCHR) Table 6-12. OCHR Field Descriptions

6.7.1.9 Real-Time Clock Control Register (RTCCR)

The RTCCR is used to configure the RTC oscillator.

Table 6-13. OCLR Field Descriptions

Figure 6-10. Real-Time Clock Control Register (RTCCR) Table 6-14. RTCCR Field Descriptions

6.7.1.10 Backup Watchdog Timer Control Register (BWCR)

Figure 6-11. Backup Watchdog Timer Control Register (BWCR) Table 6-15. BWCR Field Descriptions

Table 6-14. RTCCR Field Descriptions (continued)

6.8 Functional Description

6.8.1 System Clock Modes

6.8.2 Clock Operation During Reset

6.8.3 System Clock Generation

6.8.4 PLL Operation

6.8.4.1 Phase and Frequency Detector (PFD)

6.8.4.2 Charge Pump/Loop Filter

6.8.4.3 Voltage Control Output (VCO)

6.8.4.4 Multiplication Factor Divider (MFD)

6.8.4.5 PLL Lock Detection

6.8.4.6 PLL Loss of Lock Conditions

6.8.4.7 PLL Loss of Lock Reset

6.8.4.8 Loss of Clock Detection

6.8.4.9 Loss of Clock Reset

6.8.4.10 Alternate Clock Selection

6.8.4.11 Loss of Clock in Stop Mode

Table 6-19. Stop Mode Operation

Page

Page

Page

Page

Page

Chapter 7 Backup Watchdog Timer (BWT) Module

7.1 Introduction

7.1.1 Overview

7.1.2 Modes of Operation

7.1.2.1 Wait Mode

7.2 Memory Map and Register Definition

7.2.1 Memory Map

7.2.2 Register Descriptions

7.2.2.1 Backup Watchdog Timer Control Register (WCR)

Figure 7-2. Backup Watchdog Timer Control Register (WCR) Table 7-2. WCR Field Descriptions

7.2.2.2 Backup Watchdog Timer Modulus Register (WMR)

7.2.2.3 Backup Watchdog Timer Count Register (WCNTR)

7.2.2.4 Backup Watchdog Timer Service Register (WSR)

7.3 Functional Description

Chapter 8 Power Management

8.1 Introduction

This chapter explains the low-power operation of the MCF52211.

8.1.1 Features

8.2 Memory Map/Register Definition

8.2.1 Peripheral Power Management Registers (PPMRH, PPMRL)

Table 8-2. PPMRH Field Descriptions

8.2.1.1 Peripheral Power Management Register Low (PPMRL)

Figure 8-2. Peripheral Power Management Register Low (PPMRL) Table 8-3. PPMRL Field Descriptions

8.2.2 Low-Power Interrupt Control Register (LPICR)

Table 8-3. PPMRL Field Descriptions (continued)

Page

8.2.3 Peripheral Power Management Set Register (PPMRS)

Table 8-4. LPICR Field Description (continued)

Table 8-5. XLPM_IPL Settings

Figure 8-4. Peripheral Power Management Set Register (PPMRS) Table 8-6. PPMRS Field Descriptions

8.2.4 Peripheral Power Management Clear Register (PPMRC)

8.2.5 Low-Power Control Register (LPCR)

8.3 IPS Bus Timeout Monitor

8.4 Functional Description

8.4.1 Low-Power Modes

8.4.1.1 Run Mode

8.4.1.2 Wait Mode

8.4.1.3 Doze Mode

8.4.1.4 Stop Mode

8.4.1.5 Peripheral Shut Down

8.4.2 Peripheral Behavior in Low-Power Modes

8.4.2.1 ColdFire Core

8.4.2.2 Static Random-Access Memory (SRAM)

8.4.2.3 System Control Module (SCM)

8.4.2.4 DMA Controller (DMA0DMA3)

8.4.2.6 I2C Module

8.4.2.7 Queued Serial Peripheral Interface (QSPI)

8.4.2.8 DMA Timers (DTIM0DTIM3)

8.4.2.9 Interrupt Controllers (INTC0, INTC1)

8.4.2.10 I/O Ports

8.4.2.11 Reset Controller

8.4.2.12 Chip Configuration Module

8.4.2.13 Clock Module

8.4.2.14 Edge Port

8.4.3 Summary of Peripheral State During Low-Power Modes

Table 8-10. CPU and Peripherals in Low-Power Modes (continued)

Chapter 9 Chip Configuration Module (CCM)

9.1 Introduction

9.1.1 Features

9.2 External Signal Descriptions

9.3 Memory Map/Register Definition

9.3.2 Memory Map

9.3.3 Register Descriptions

9.3.3.1 Chip Configuration Register (CCR)

The following section describes the CCM registers.

Table 9-3. Chip Configuration Module Memory Map

9.3.3.2 Reset Configuration Register (RCON)

Figure 9-3. Chip Identification Register (CIR)

9.3.3.3 Chip Identification Register (CIR)

Figure 9-2. Reset Configuration Register (RCON) Table 9-5. RCON Field Descriptions

Table 9-6. CIR Field Description

Page

Chapter 10 Reset Controller Module

10.1 Introduction

10.2 Features

10.3 Block Diagram

10.4 Signals

10.4.1 RSTI

10.4.2 RSTO

10.5 Memory Map and Registers

See Table 10-2 for the memory map and the following paragraphs for a description of the registers.

10.5.1 Reset Control Register (RCR)

Table 10-2. Reset Controller Memory Map

Figure 10-2. Reset Control Register (RCR) Table 10-3. RCR Field Descriptions

10.5.2 Reset Status Register (RSR)

Figure 10-3. Reset Status Register (RSR) Table 10-4. RSR Field Descriptions

Table 10-3. RCR Field Descriptions (continued)

10.6 Functional Description

10.6.1 Reset Sources

Table 10-5 defines the sources of reset and the signals driven by the reset controller.

Table 10-5. Reset Source Summary

Table 10-4. RSR Field Descriptions (continued)

10.6.1.1 Power-On Reset

10.6.1.2 External Reset

10.6.1.3 Loss-of-Clock Reset

10.6.1.4 Loss-of-Lock Reset

10.6.1.5 Software Reset

Page

Figure 10-4. Reset Control Flow

10-8 Freescale Semiconductor

10.6.2.1 Synchronous Reset Requests

10.6.2.2 Internal Reset Request

10.6.2.3 Power-On Reset/Low-Voltage Detect Reset

10.6.3 Concurrent Resets

10.6.3.1 Reset Flow

10.6.3.2 Reset Status Flags

Chapter 11 Real-Time Clock

11.1 Introduction

11.1.1 Overview

11.1.2 Features

11.1.3 Modes of Operation

11.2 Memory Map/Register Definition

11.2.1 Register Descriptions

11.2.1.1 RTC Hours and Minutes Counter Register (HOURMIN)

Figure 11-2. RTC Hours and Minutes Counter Register (HOURMIN)

Table 11-2. HOURMIN Field Descriptions

11.2.1.2 RTC Seconds Counter Register (SECONDS)

Figure 11-3. RTC Seconds Counter Register (SECONDS)

Table 11-3. SECONDS Field Descriptions

11.2.1.3 RTC Hours and Minutes Alarm Register (ALRM_HM)

Figure 11-4. RTC Hours and Minutes Alarm Register (ALRM_HM)

Table 11-4. ALRM_HM Field Descriptions

11.2.1.4 RTC Seconds Alarm Register (ALRM_SEC)

Figure 11-5. RTC Seconds Alarm Register (ALRM_SEC)

Table 11-5. ALRM_SEC Field Descriptions

11.2.1.5 RTC Control Register (RTCCTL)

Figure 11-6. RTC Control Register (RTCCTL)

Table 11-6. RTCCTL Field Descriptions

11.2.1.6 RTC Interrupt Status Register (RTCISR)

Figure 11-7. RTC Interrupt Status Register (RTCISR)

Table 11-7. RTCISR Field Descriptions

11.2.1.7 RTC Interrupt Enable Register (RTCIENR)

Figure 11-8. RTC Interrupt Enable Register (RTCIENR)

Table 11-8. RTCIENR Field Descriptions

11.2.1.8 RTC Stopwatch Minutes Register (STPWCH)

Figure 11-9. RTC Stopwatch Minutes Register (STPWCH)

Table 11-9. STPWCH Field Descriptions

11.2.1.9 RTC Days Counter Register (DAYS)

Figure 11-10. RTC Days Counter Register (DAYS)

Table 11-10. DAYS Field Descriptions

11.2.1.10 RTC Day Alarm Register (ALRM_DAY)

Figure 11-12. RTC General Oscillator Count Upper Register (RTCGOCU)

Figure 11-11. RTC Day Alarm Register (ALRM_DAY)

11.2.1.11 RTC General Oscillator Count Registers (RTCGOCU and RTCGOCL)

Table 11-11. ALRM_DAY Field Descriptions

11.3 Functional Description

11.3.1 Prescaler and Counter

11.3.2 Alarm

11.3.3 Minute Stopwatch

11.4 Initialization/Application Information

11.4.1 Flow Chart of RTC Operation

Figure 11-14. Flow Chart of RTC Operation

11.4.2 Code Example for Initializing the Real-Time Clock

Figure 11-15. Code Example for Initializing the Real-Time Clock

Figure 11-15 shows sample code for initializing the RTC.

Page

Chapter 12 System Control Module (SCM)

12.1 Introduction

12.2 Overview

12.3 Features

12.4 Memory Map and Register Definition

Table 12-1. SCM Register Map

12.5 Register Descriptions

12.5.1 Internal Peripheral System Base Address Register (IPSBAR)

Table 12-2. Accessing as 32-Bit Registers

Table 12-1. SCM Register Map (continued)

12.5.2 Memory Base Address Register (RAMBAR)

Page

12.5.3 Core Reset Status Register (CRSR)

12.5.4 Core Watchdog Control Register (CWCR)

12.5.5 Core Watchdog Service Register (CWSR)

Table 12-6. CWCR Field Description

12.6 Internal Bus Arbitration

12.6.1 Overview

12.6.2 Arbitration Algorithms

12.6.2.1 Round-Robin Mode

12.6.2.2 Fixed Mode

12.6.3 Bus Master Park Register (MPARK)

Master 2 (M2): 4-channel DMA Master 0 (M0): V2 ColdFire Core

Figure 12-7. Default Bus Master Park Register (MPARK) Table 12-7. MPARK Field Description

12.7 System Access Control Unit (SACU)

12.7.1 Overview

12.7.2 Features

12.7.3 Memory Map/Register Definition

12.7.3.1 Master Privilege Register (MPR)

12.7.3.2 Peripheral Access Control Registers (PACR0PACR8)

Figure 12-9. Peripheral Access Control Register (PACRn) Table 12-10. PACR Field Descriptions

Table 12-11. PACR ACCESSCTRL Bit Encodings

Table 12-12. Peripheral Access Control Registers (PACRs)

12.7.3.3 Grouped Peripheral Access Control Registers (GPACR0 & GPACR1)

Table 12-13. Grouped Peripheral Access Control Register (GPACR) Field Descriptions

Table 12-14. GPACR ACCESS_CTRL Bit Encodings

Table 12-15. GPACR Address Space

Freescale Semiconductor 13-1

Chapter 13 General Purpose I/O Module

13.1 Introduction

Figure 13-1. General Purpose I/O Module Block Diagram

13.2 Overview

13.3 Features

13.4 Signal Descriptions

13.5 Memory Map/Register Definition

13.5.1 Ports Memory Map

Table 13-1. Registers in the MCF52211 Ports Address Space Address

3124 2316 158 70 Access

13.6 Register Descriptions

13.6.1 Port Output Data Registers (PORTn)

13.6.2 Port Data Direction Registers (DDRn)

Figure 13-4. Port QS Output Data Register (PORTQS)

Figure 13-5. Port NQ Output Data Register (PORTNQ)

Figure 13-6. Port AS Output Data Register (PORTAS) Table 13-2. PORTn Field Descriptions

Figure 13-7. Port Data Direction Registers with Bits 7:0 Implemented (DDRDD, DDRAN)

Figure 13-10. Port NQ Data Direction Register (DDRNQ)

Figure 13-9. Port QS Data Direction Register (DDRQS)

13.6.3 Port Pin Data/Set Data Registers (PORTnP/SETn)

Figure 13-14. Port QS Pin Data/Set Data Register (PORTQS/SETQS)

Figure 13-16. Port AS Pin Data/Set Data Register (PORTAS/SETAS)

Figure 13-15. Port NQ Pin Data/Set Data Register (PORTNQ/SETNQ)

13.6.4 Port Clear Output Data Registers (CLRn)

Table 13-4. PORTnP/SETn Field Descriptions

Figure 13-17. Port Clear Output Data Registers with Bits 7:0 Implemented (CLRDD, CLRAN)

13.6.5 Pin Assignment Registers

Figure 13-19. Port QS Clear Output Data Register (CLRQS)

Figure 13-20. Port NQ Clear Output Data Register (CLRNQ)

Figure 13-21. Port AS Clear Output Data Register (CLRAS) Table 13-5. CLRn Field Descriptions

13.6.5.1 Dual-Function Pin Assignment Registers

13.6.5.2 Quad Function Pin Assignment Registers

Figure 13-22. Dual-Function Pin Assignment Registers with Bits 7:0 Implemented (PDDPAR, PANPAR)

Figure 13-24. Port QS Pin Assignment Register (PQSPAR)

Figure 13-25. Port AS Pin Assignment Register (PASPAR)

13.6.5.3 Port NQ Pin Assignment Register (PNQPAR)

13.6.6 Pad Control Registers

13.6.6.1 Pin Slew Rate Register (PSRR)

Figure 13-28. Pin Slew Rate Register (PSRR) Table 13-8. PSRR Field Descriptions

13.6.6.2 Pin Drive Strength Register (PDSR)

The ports module does not generate interrupt requests.

13.7 Ports Interrupts

Figure 13-29. Pin Drive Strength Register (PDSR) Table 13-9. PDSR Field Descriptions

Page

Chapter 14 Interrupt Controller Module

14.1 68K/ColdFire Interrupt Architecture Overview

14.1.1 Interrupt Controller Theory of Operation

14.1.1.1 Interrupt Recognition

14.1.1.2 Interrupt Prioritization

14.1.1.3 Interrupt Vector Determination

14.2 Memory Map

14.3 Register Descriptions

The interrupt controller registers are described in the following sections.

Table 14-2. Interrupt Controller Memory Map (continued)

14.3.1 Interrupt Pending Registers (IPRHn, IPRLn)

Figure 14-2. Interrupt Pending Register Low (IPRLn)

Figure 14-1. Interrupt Pending Register High (IPRHn) Table 14-3. IPRHn Field Descriptions

14.3.2 Interrupt Mask Register (IMRHn, IMRLn)

Table 14-4. IPRLn Field Descriptions

Figure 14-3. Interrupt Mask Register High (IMRHn) Table 14-5. IMRHn Field Descriptions

14.3.3 Interrupt Force Registers (INTFRCHn, INTFRCLn)

Figure 14-5. Interrupt Force Register High (INTFRCHn) Table 14-7. INTFRCHn Field Descriptions

Figure 14-6. Interrupt Force Register Low (INTFRCLn) Table 14-8. INTFRCLn Field Descriptions

14.3.4 Interrupt Request Level Register (IRLRn)

14.3.5 Interrupt Acknowledge Level and Priority Register (IACKLPRn)

14.3.6 Interrupt Control Registers (ICRnx)

Figure 14-9. Interrupt Control Register (ICRnx) Table 14-12. ICRnx Field Descriptions

14.3.6.1 Interrupt Sources

Table 14-13 lists the interrupt sources for each interrupt request line.

Page

14.3.7 Software and Level m IACK Registers (SWIACKn, LmIACKn)

14.3.8 Global Level m IACK Registers (GLmIACK)

14.4 Low-Power Wakeup Operation

Page

Page

Chapter 15 Universal Serial Bus, OTG Capable Controller

15.1 Introduction

15.1.1 USB

Page

15.1.2 USB On-The-Go

15.1.3 USB-FS Features

15.2 Functional Description

15.2.1 Data Structures

15.3 Programmers Interface 15.3.1 Buffer Descriptor Table

15.3.2 Rx vs. Tx as a USB Target Device or USB Host

15.3.3 Addressing Buffer Descriptor Table Entries

15.3.4 Buffer Descriptor Formats

Figure 15-5. Buffer Descriptor Byte Format

Table 15-3. Buffer Descriptor Byte Fields

15.3.5 USB Transaction

15.4 Memory Map/Register Definitions

The following sections provide details about the registers in the USB OTG memory map.

15.4.1 Capability Registers

15.4.1.1 Peripheral ID Register (PER_ID)

Table 15-4. USB Interface Memory Map (continued)

15.4.1.2 Peripheral ID Complement Register (ID_COMP)

Figure 15-7. Peripheral ID Register (PER_ID) Table 15-11. PER_ID Field Descriptions

Figure 15-8. Peripheral ID Complement Register Table 15-12. ID_COMP Field Descriptions

15.4.1.3 Peripheral Revision Register (REV)

This register contains the revision number of the USB Module. Figure 15-9 shows the REV register.

15.4.1.4 Peripheral Additional Info Register (ADD_INFO)

Figure 15-9. Peripheral Revision Register Table 15-13. REV Field Descriptions

Figure 15-10. Peripheral Additional Info Register Table 15-14. ADD_INFO Field Descriptions

15.4.1.5 OTG Interrupt Status Register (OTG_INT_STAT)

Figure 15-11. OTG Interrupt Status Register Table 15-15. OTG_INT_STAT Field Descriptions

15.4.1.6 OTG Interrupt Control Register (OTG_INT_EN)

Figure 15-12. OTG Interrupt Control Register Table 15-16. OTG_INT_EN Field Descriptions

15.4.1.7 Interrupt Status Register (OTG_STAT)

Figure 15-13. Interrupt Status Register Table 15-17. OTG_STAT Field Descriptions

15.4.1.8 OTG Control Register (OTG_CTRL)

Figure 15-14. OTG Control Register Table 15-18. OTG_CTRL Field Descriptions

15.4.1.9 Interrupt Status Register (INT_STAT)

Figure 15-15. Interrupt Status Register Table 15-19. INT_STAT Field Descriptions

15.4.1.10 Interrupt Enable Register (INT_ENB)

Figure 15-16. Interrupt Enable Register Table 15-20. INT_ENB Field Descriptions

15.4.1.11 Error Interrupt Status Register (ERR_STAT)

Figure 15-17. Error Interrupt Status Register Table 15-21. ERR_STAT Field Descriptions

15.4.1.12 Error Interrupt Enable Register (ERR_ENB)

Figure 15-18. Error Interrupt Enable Register Table 15-22. ERR_ENB Field Descriptions

15.4.1.13 Status Register (STAT)

15.4.1.14 Control Register (CTL)

Figure 15-20. Control Register Table 15-24. CTL Field Descriptions

15.4.1.15 Address Register (ADDR)

15.4.1.16 BDT Page Register 1 (BDT_PAGE_01)

Figure 15-22. BDT_PAGE_01 Register Table 15-26. BDT_PAGE_01 Field Descriptions

15.4.1.17 Frame Number Register Low/High (FRM_NUML, FRM_NUMH)

Figure 15-23. FRM_NUML Register Table 15-27. FRM_NUML Field Descriptions

Figure 15-24. FRM_NUMH Register Table 15-28. FRM_NUMH Field Descriptions

15.4.1.18 Token Register (TOKEN)

15.4.1.19 SOF Threshold Register (SOF_THLD)

15.4.1.20 BDT Page Register 2 (BDT_PAGE_02)

15.4.1.21 BDT Page Register 3 (BDT_PAGE_03)

Figure 15-27. BDT_PAGE_02 Register Table 15-31. BDT_PAGE_02 Field Descriptions

Figure 15-28. BDT_PAGE_03 Register Table 15-32. BDT_PAGE_03 Field Descriptions

15.4.1.22 Endpoint Control Registers 0 15 (ENDPT015)

Figure 15-29. BDT_PAGE_03 Register Table 15-33. BDT_PAGE_03 Field Descriptions

Table 15-34. Endpoint Direction and Control

Table 15-33. BDT_PAGE_03 Field Descriptions (continued)

15.4.1.23 USB Control Register (USB_CTRL)

Figure 15-30. USB Control Register Table 15-35. USB_CTRL Field Descriptions

15.4.1.24 USB OTG Observe Register (USB_OTG_OBSERVE)

Figure 15-31. USB OTG Observe Register Table 15-36. USB_OTG_OBSERVE Field Descriptions

15.4.1.25 USB OTG Control Register (USB_OTG_CONTROL)

15.5 OTG and Host Mode Operation

Figure 15-32. USB OTG Control Register Table 15-37. USB_OTG_CONTROL Field Descriptions

15.6 Host Mode Operation Examples

Page

15.7 On-The-Go Operation

15.7.1 OTG Dual Role A Device Operation

Figure 15-33. Dual Role A Device Flow Diagram Table 15-38. State Descriptions for Figure 15-33

15.7.2 OTG Dual Role B Device Operation

Figure 15-34. Dual Role B Device Flow Diagram

Table 15-39. State Descriptions for Figure 15-34

Table 15-38. State Descriptions for Figure 15-33 (continued)

15.7.3 Power

15.7.4 USB Suspend State

Chapter 16 Edge Port Module (EPORT)

16.1 Introduction

16.2 Low-Power Mode Operation

16.3 Interrupt/GPIO Pin Descriptions

16.4 Memory Map/Register Definition

16.4.1 EPORT Pin Assignment Register (EPPAR)

The EPORT pin assignment register (EPPAR) controls the function of each pin individually.

Table 16-2. Edge Port Module Memory Map

Figure 16-2. EPORT Pin Assignment Register (EPPAR) Table 16-3. EPPAR Field Descriptions

16.4.2 EPORT Data Direction Register (EPDDR)

The EPORT interrupt enable register (EPIER) enables interrupt requests for each pin individually.

16.4.3 Edge Port Interrupt Enable Register (EPIER)

Figure 16-3. EPORT Data Direction Register (EPDDR) Table 16-4. EPDDR Field Descriptions

Figure 16-4. EPORT Port Interrupt Enable Register (EPIER) Table 16-5. EPIER Field Descriptions

16.4.4 Edge Port Data Register (EPDR)

The EPORT data register (EPDR) holds the data to be driven to the pins.

The EPORT pin data register (EPPDR) reflects the current state of the pins.

16.4.5 Edge Port Pin Data Register (EPPDR)

Figure 16-5. EPORT Port Data Register (EPDR) Table 16-6. EPDR Field Descriptions

16.4.6 Edge Port Flag Register (EPFR)

The EPORT flag register (EPFR) individually latches EPORT edge events.

Figure 16-7. EPORT Port Flag Register (EPFR) Table 16-8. EPFR Field Descriptions

Chapter 17 DMA Controller Module

17.1 Introduction

17.1.1 Overview

17.1.2 Features

17.2 DMA Transfer Overview

17.3 Memory Map/Register Definition

17.3.1 DMA Request Control (DMAREQC)

Figure 17-3. DMA Request Control Register (DMAREQC)

Table 17-1. Memory Map for DMA Controller Module Registers

17.3.2 Source Address Registers (SARn)

SARn, shown in Figure 17-4, contains the address from which the DMA controller requests data.

Figure 17-4. Source Address Registers (SARn)

DARn, shown in Figure 17-5, holds the address to which the DMA controller sends data.

17.3.3 Destination Address Registers (DARn)

17.3.4 Byte Count Registers (BCRn) and DMA Status Registers (DSRn)

Figure 17-7. DMA Status Registers (DSRn) Table 17-3. DSRn Field Descriptions

17.3.5 DMA Control Registers (DCRn)

The DMA control registers (DCRn) are described in Figure 17-8 and Table 17-4.

Figure 17-8. DMA Control Registers (DCRn) Table 17-4. DCRn Field Descriptions

Page

Table 17-4. DCRn Field Descriptions (continued)

17.4 Functional Description

17.4.1 Transfer Requests (Cycle-Steal and Continuous Modes)

17.4.2 Dual-Address Data Transfer Mode

17.4.3 Channel Initialization and Startup

17.4.3.1 Channel Prioritization

17.4.3.2 Programming the DMA Controller Module

17.4.4 Data Transfer

17.4.4.1 Auto-Alignment

17.4.4.2 Bandwidth Control

17.4.5 Termination

Page

Chapter 18 ColdFire Flash Module (CFM)

18.1 Introduction

18.1.1 Overview

18.1.2 Features

COMMON FLASH BUS

INTERNAL FLASH BUS

18.2 External Signal Description

18.3 Memory Map and Register Definition

18.3.1 Memory Map

18.3.2 Flash Base Address Register (FLASHBAR)

Page

Table 18-2. FLASHBAR Field Descriptions

Table 18-3. CFM Register Address Map

18.3.3 Register Descriptions

18.3.3.1 CFMMCR CFM Module Configuration Register

The CFMMCR register is used to configure and control the operation of the internal bus interface.

Figure 18-4. CFM Module Configuration Register (CFMMCR) Table 18-4. CFMMCR Field Descriptions

Table 18-3. CFM Register Address Map

18.3.3.2 CFMCLKD CFM Clock Divider Register

Figure 18-5. CFM Clock Divider Register (CFMCLKD)

Table 18-4. CFMMCR Field Descriptions (continued)

All CFMCLKD register bits are readable, while bits [6:0] write once and bit 7 is not writable.

18.3.3.3 CFMSEC CFM Security Register

The CFMSEC register is used to store the flash security word and CFM security state.

Table 18-5. CFMCLKD Field Descriptions

Figure 18-6. CFM Security Register (CFMSEC) Table 18-6. CFMSEC Field Descriptions

The CFM flash security operation is described in Section 18.4.3, Flash Security Operation.

18.3.3.4 CFMPROT CFM Protection Register

Figure 18-7. CFM Protection Register (CFMPROT)

Table 18-7. CFM Security States

Table 18-6. CFMSEC Field Descriptions

SECTOR 0

PROTECT[31:0]

SECTOR 16

SECTOR 15

18.3.3.5 CFMSACC CFM Supervisor Access Register

The CFMSACC register is used to control supervisor/user access to the flash memory.

Figure 18-9. CFM Supervisor Access Register (CFMSACC)

Table 18-9.

18.3.3.6 CFMDACC CFM Data Access Register

The CFMDACC register is used to control data/instruction access to the flash memory.

Figure 18-11. CFM User Status Register (CFMUSTAT)

Figure 18-10. CFM Data Access Register (CFMDACC)

18.3.3.7 CFMUSTAT CFM User Status Register

Only one CFMUSTAT register bit can be cleared at a time.

Table 18-11. CFMUSTAT Field Descriptions

18.3.3.8 CFMCMD CFM Command Register

The CFMCMD register is the flash command register.

Figure 18-12. CFM Command Buffer and Register (CFMCMD)

Table 18-12. CFMCMD Field Descriptions

Table 18-13. CFM Flash Memory Commands

18.4 Functional Description

18.4.1 General

18.4.2 Flash Normal Mode

18.4.2.1 Read Operation

18.4.2.2 Write Operation

18.4.2.3 Program, Erase, and Verify Operations

Page

Page

18-20 Freescale Semiconductor

Figure 18-14. Example Blank Check Command Flow

START

Page

18-22 Freescale Semiconductor

Figure 18-15. Example Page Erase Verify Command Flow

START

Page

18-24 Freescale Semiconductor

Figure 18-16. Example Program Command Flow

Page

18-26 Freescale Semiconductor

Figure 18-17. Example Page Erase Command Flow

Mass Erase The mass erase operation erases all flash memory addresses using an embedded algorithm.

Page

Figure 18-18. Example Mass Erase Command Flow

18-28 Freescale Semiconductor

18.4.2.4 Stop Mode

18.4.3 Flash Security Operation

18.4.3.1 Backdoor Access Sequence

Page

Page

Chapter 19 EzPort

19.1 Features

19.2 Modes of Operation

Figure 19-1 is a block diagram of the EzPort.

Figure 19-1. EzPort Block Diagram

19.3 External Signal Description

19.3.1 Overview

Table 19-1 contains a list of EzPort external signals.

19.3.2 Detailed Signal Descriptions

19.3.2.1 EZPCK EzPort Clock

19.4 Command Definition

19.4.1 Command Descriptions

19.4.1.1 Write Enable

19.4.1.2 Write Disable

19.4.1.3 Read Status Register

The Read Status Register command returns the contents of the EzPort Status register.

19.4.1.4 Write Configuration Register

Figure 19-3. EzPort Configuration Register

Table 19-3. EzPort Status Register Field Description (continued)

19.4.1.5 Read Data

19.4.1.6 Read Data at High Speed

19.4.1.7 Page Program

19.4.1.8 Sector Erase

19.4.1.9 Bulk Erase

19.5 Functional Description

19.6 Initialization/Application Information

Chapter 20 Programmable Interrupt Timers (PIT0PIT1)

20.1 Introduction

20.1.1 Overview

20.1.2 Block Diagram

20.1.3 Low-Power Mode Operation

20.2 Memory Map/Register Definition

20.2.1 PIT Control and Status Register (PCSRn)

The PCSRn registers configure the corresponding timers operation.

Figure 20-2. PCSRn Register Table 20-3. PCSRn Field Descriptions

20.2.2 PIT Modulus Register (PMRn)

Figure 20-3. PIT Modulus Register (PMRn)

Table 20-3. PCSRn Field Descriptions (continued)

20.2.3 PIT Count Register (PCNTRn)

20.3 Functional Description

20.3.1 Set-and-Forget Timer Operation

20.3.2 Free-Running Timer Operation

20.3.3 Timeout Specifications

20.3.4 Interrupt Operation

Timeout period PRE[3:0] (PM[15:0] 1)+fsys

Page

Page

Chapter 21 General Purpose Timer Module (GPT)

21.1 Introduction

21.2 Features

21-2 Freescale Semiconductor

21.3 Block Diagram

Figure 21-1. GPT Block Diagram

21.4 Low-Power Mode Operation

21.5 Signal Description

21.5.1 GPT[2:0]

21.5.2 GPT3

21.5.3 SYNCn

21.6 Memory Map and Registers

Table 21-3 shows the memory map of the GPT module. The base address for GPT is IPSBAR + 0x1A_0000.

Table 21-3. GPT Memory Map

21.6.1 GPT Input Capture/Output Compare Select Register (GPTIOS)

Table 21-3. GPT Memory Map (continued)

21.6.2 GPT Compare Force Register (GPCFORC)

Figure 21-4. GPT Output Compare 3 Mask Register (GPTOC3M)

21.6.3 GPT Output Compare 3 Mask Register (GPTOC3M)

Figure 21-3. GPT Input Compare Force Register (GPCFORC) Table 21-5. GPTCFORC Field Descriptions

21.6.4 GPT Output Compare 3 Data Register (GPTOC3D)

Figure 21-6. GPT Counter Register (GPTCNT)

21.6.5 GPT Counter Register (GPTCNT)

Table 21-6. GPTOC3M Field Descriptions

Figure 21-5. GPT Output Compare 3 Data Register (GPTOC3D) Table 21-7. GPTOC3D Field Descriptions

21.6.6 GPT System Control Register 1 (GPTSCR1)

Table 21-8. GPTCNT Field Descriptions

Figure 21-7. GPT System Control Register 1 (GPTSCR1) Table 21-9. GPTSCR1 Field Descriptions

Figure 21-8. Fast Clear Flag Logic

21.6.7 GPT Toggle-On-Overflow Register (GPTTOV)

21.6.8 GPT Control Register 1 (GPTCTL1)

Figure 21-9. GPT Toggle-On-Overflow Register (GPTTOV) Table 21-10. GPTTOV Field Description

Figure 21-10. GPT Control Register 1 (GPTCTL1)

21.6.9 GPT Control Register 2 (GPTCTL2)

21.6.10 GPT Interrupt Enable Register (GPTIE)

Figure 21-12. GPT Interrupt Enable Register (GPTIE)

Table 21-11. GPTCL1 Field Descriptions

Figure 21-11. GPT Control Register 2(GPTCTL2) Table 21-12. GPTLCTL2 Field Descriptions

21.6.11 GPT System Control Register 2 (GPTSCR2)

Table 21-13. GPTIE Field Descriptions

Figure 21-13. GPT System Control Register 2 (GPTSCR2) Table 21-14. GPTSCR2 Field Descriptions

21.6.12 GPT Flag Register 1 (GPTFLG1)

21.6.13 GPT Flag Register 2 (GPTFLG2)

Figure 21-15. GPT Flag Register 2 (GPTFLG2)

Figure 21-14. GPT Flag Register 1 (GPTFLG1) Table 21-15. GPTFLG1 Field Descriptions

Table 21-14. GPTSCR2 Field Descriptions (continued)

21.6.14 GPT Channel Registers (GPTCn)

21.6.15 Pulse Accumulator Control Register (GPTPACTL)

Figure 21-17. Pulse Accumulator Control Register (GPTPACTL)

Table 21-16. GPTFLG2 Field Descriptions

Figure 21-16. GPT Channel[0:3] Register (GPTCn) Table 21-17. GPTCn Field Descriptions

21.6.16 Pulse Accumulator Flag Register (GPTPAFLG)

Table 21-18. GPTPACTL Field Descriptions

Figure 21-18. Pulse Accumulator Flag Register (GPTPAFLG)

21.6.17 Pulse Accumulator Counter Register (GPTPACNT)

Table 21-19. GPTPAFLG Field Descriptions

Figure 21-19. Pulse Accumulator Counter Register (GPTPACNT) Table 21-20. GPTPACR Field Descriptions

21.6.18 GPT Port Data Register (GPTPORT)

21.6.19 GPT Port Data Direction Register (GPTDDR)

21.7 Functional Description

Figure 21-20. GPT Port Data Register (GPTPORT) Table 21-21. GPTPORT Field Descriptions

Figure 21-21. GPT Port Data Direction Register (GPTDDR) Table 21-22. GPTDDR Field Descriptions

21.7.1 Prescaler

21.7.2 Input Capture

21.7.3 Output Compare

21.7.4 Pulse Accumulator

21.7.5 Event Counter Mode

21.7.6 Gated Time Accumulation Mode

21.7.7 General-Purpose I/O Ports

Table 21-23. GPT Settings and Pin Functions

21.8 Reset

21.9 Interrupts

21.9.1 GPT Channel Interrupts (CnF)

21.9.2 Pulse Accumulator Overflow (PAOVF)

21.9.3 Pulse Accumulator Input (PAIF)

21.9.4 Timer Overflow (TOF)

Chapter 22 DMA Timers (DTIM0DTIM3)

22.1 Introduction

22.1.1 Overview

22.1.2 Features

22.2 Memory Map/Register Definition

22.2.1 DMA Timer Mode Registers (DTMRn)

DTMRs, shown in Figure 22-2, program the prescaler and various timer modes.

Figure 22-2. DTMRn Registers

Table 22-1. DMA Timer Module Memory Map

22.2.2 DMA Timer Extended Mode Registers (DTXMRn)

The DTXMRn register programs DMA request and increment modes for the timers.

Figure 22-3. DTXMRn Registers

Table 22-2. DTMRn Field Descriptions

22.2.3 DMA Timer Event Registers (DTERn)

Figure 22-4. DTERn Registers

Table 22-3. DTXMRn Field Descriptions

22.2.4 DMA Timer Reference Registers (DTRRn)

Table 22-4. DTERn Field Descriptions

22.2.5 DMA Timer Capture Registers (DTCRn)

22.2.6 DMA Timer Counters (DTCNn)

Figure 22-5. DTRRn Registers Table 22-5. DTRRn Field Descriptions

Figure 22-6. DTCRn Registers Table 22-6. DTCRn Field Descriptions

22.3 Functional Description

22.3.1 Prescaler

22.3.2 Capture Mode

22.3.3 Reference Compare

22.3.4 Output Mode

22.4 Initialization/Application Information

22.4.1 Code Example

22.4.2 Calculating Time-Out Values

-------------------- 16 127 1+()64453 1+() 2.00 s==

Equation 22-1 determines time-out periods for various reference values:

Eqn. 22-1

Eqn. 22-2

Chapter 23 Queued Serial Peripheral Interface (QSPI)

23.1 Introduction

Figure 23-1. QSPI Block Diagram

23.1.1 Block Diagram

Figure 23-1 illustrates the QSPI module.

23.2 External Signal Description

23.3 Memory Map/Register Definition

23.3.1 QSPI Mode Register (QMR)

Table 23-3. QMR Field Descriptions

Figure 23-3 shows an example of a QSPI clocking and data transfer.

Figure 23-3. QSPI Clocking and Data Transfer Example

23.3.2 QSPI Delay Register (QDLYR)

The QDLYR is used to initiate master mode transfers and to set various delay parameters.

Figure 23-4. QSPI Delay Register (QDLYR) Table 23-4. QDLYR Field Descriptions

23.3.3 QSPI Wrap Register (QWR)

Figure 23-6. QSPI Interrupt Register (QIR)

The QIR contains QSPI interrupt enables and status flags.

23.3.4 QSPI Interrupt Register (QIR)

Figure 23-5. QSPI Wrap Register (QWR) Table 23-5. QWR Field Descriptions

23.3.5 QSPI Address Register (QAR)

Table 23-6. QIR Field Descriptions

23.3.6 QSPI Data Register (QDR)

23.3.7 Command RAM Registers (QCR0QCR15)

Figure 23-7. QSPI Address Register (QAR) Table 23-7. QAR Field Descriptions

Figure 23-8. QSPI Data Register (QDR) Table 23-8. QDR Field Descriptions

23.4 Functional Description

Figure 23-9. Command RAM Registers (QCR0QCR15) Table 23-9. QCR0QCR15 Field Descriptions

Page

23.4.1 QSPI RAM

23.4.1.1 Receive RAM

23.4.1.2 Transmit RAM

23.4.1.3 Command RAM

23.4.2 Baud Rate Selection

23.4.3 Transfer Delays

23.4.4 Transfer Length

23.4.5 Data Transfer

23.5 Initialization/Application Information

Page

Chapter 24 UART Modules

24.1 Introduction

24.1.1 Overview

24.1.2 Features

24.2 External Signal Description

24.3 Memory Map/Register Definition

Table 24-2. UART Module Memory Map

24.3.1 UART Mode Registers 1 (UMR1n)

Figure 24-3. UART Mode Registers 1 (UMR1n) Table 24-3. UMR1n Field Descriptions

24.3.2 UART Mode Register 2 (UMR2n)

Figure 24-4. UART Mode Registers 2 (UMR2n)

Table 24-3. UMR1n Field Descriptions (continued)

24.3.3 UART Status Registers (USRn)

Table 24-4. UMR2n Field Descriptions

Figure 24-5. UART Status Registers (USRn) Table 24-5. USRn Field Descriptions

24.3.4 UART Clock Select Registers (UCSRn)

TRANSMITTER cannot be specified in one command.

24.3.5 UART Command Registers (UCRn)

Figure 24-6. UART Clock Select Registers (UCSRn) Table 24-6. UCSRn Field Descriptions

Table 24-5. USRn Field Descriptions (continued)

Figure 24-7. UART Command Registers (UCRn) Table 24-7. UCRn Field Descriptions

24.3.6 UART Receive Buffers (URBn)

Table 24-7. UCRn Field Descriptions (continued)

24.3.7 UART Transmit Buffers (UTBn)

24.3.8 UART Input Port Change Registers (UIPCRn)

24.3.9 UART Auxiliary Control Register (UACRn)

The UACRs control the input enable.

24.3.10 UART Interrupt Status/Mask Registers (UISRn/UIMRn)

Table 24-8. UIPCRn Field Descriptions

Figure 24-11. UART Auxiliary Control Registers (UACRn) Table 24-9. UACRn Field Descriptions

Page

24.3.11 UART Baud Rate Generator Registers (UBG1n/UBG2n)

Figure 24-15. UART Input Port Registers (UIPn)

The UIPn registers, shown in Figure 24-15, show the current state of the UCTSn input.

24.3.12 UART Input Port Register (UIPn)

Figure 24-13. UART Baud Rate Generator Registers (UBG1n)

24.4 Functional Description

This section describes operation of the clock source generator, transmitter, and receiver.

24.4.1 Transmitter/Receiver Clock Source

Table 24-11. UIPn Field Descriptions

24.4.1.1 Programmable Divider

clock; when divided by 16, it is asynchronous.

24.4.1.2 Calculating Baud Rates

24.4.2 Transmitter and Receiver Operating Modes

24.4.2.1 Transmitter

Page

24.4.2.2 Receiver

24.4.2.3 FIFO

24.4.3 Looping Modes

24.4.3.1 Automatic Echo Mode

24.4.3.2 Local Loopback Mode

24.4.3.3 Remote Loopback Mode

24.4.4 Multidrop Mode

Page

24.4.5 Bus Operation

24.4.5.1 Read Cycles

24.4.5.2 Write Cycles

24.5 Initialization/Application Information

24.5.1 Interrupt and DMA Request Initialization

24.5.1.1 Setting up the UART to Generate Core Interrupts

24.5.1.2 Setting up the UART to Request DMA Service

24.5.2 UART Module Initialization Sequence

Freescale Semiconductor 24-29

Figure 24-25. UART Mode Programming Flowchart (Sheet 1 of 5)

Figure 24-25. UART Mode Programming Flowchart (Sheet 2 of 5)

24-30 Freescale Semiconductor

Figure 24-25. UART Mode Programming Flowchart (Sheet 3 of 5)

Freescale Semiconductor 24-31

Figure 24-25. UART Mode Programming Flowchart (Sheet 4 of 5)

24-32 Freescale Semiconductor

Figure 24-25. UART Mode Programming Flowchart (Sheet 5 of 5)

Page

Chapter 25 I2C Interface

25.1 Introduction

25.1.1 Block Diagram

25.1.2 Overview

25.1.3 Features

25.2 Memory Map/Register Definition

25.2.1 I2C Address Registers (I2ADRn)

25.2.2 I2C Frequency Divider Registers (I2FDRn)

Table 25-1. I2C Module Memory Map

Figure 25-2. I2ADRn Registers Table 25-2. I2ADRn Field Descriptions

25.2.3 I2C Control Registers (I2CRn)

Figure 25-3. I2FDRn Registers Table 25-3. I2FDRn Field Descriptions

Figure 25-4. I2CRn Registers Table 25-4. I2CRn Field Descriptions

25.2.4 I2C Status Registers (I2SRn)

The I2SRn contain bits that indicate transaction direction and status.

Figure 25-5. I2SRn Registers Table 25-5. I2SRn Field Descriptions

25.2.5 I2C Data I/O Registers (I2DRn)

25.3 Functional Description

25.3.1 START Signal

25.3.2 Slave Address Transmission

25.3.3 Data Transfer

25.3.4 Acknowledge

25.3.5 STOP Signal

25.3.6 Repeated START

Figure 25-10. Repeated START

Figure 25-11. Data Transfer, Combined Format

25.3.7 Clock Synchronization and Arbitration

25.3.8 Handshaking and Clock Stretching

25.4 Initialization/Application Information

25.4.1 Initialization Sequence

25.4.2 Generation of START

25.4.3 Post-Transfer Software Response

25.4.4 Generation of STOP

25.4.5 Generation of Repeated START

25.4.6 Slave Mode

25.4.7 Arbitration Lost

Figure 25-14. Flow-Chart of Typical I2C Interrupt Routine

Chapter 26 Analog-to-Digital Converter (ADC)

26.1 Introduction

26.2 Features

26.3 Block Diagram

Figure 26-1. Dual ADC Block Diagram

26.4 Memory Map and Register Definition

Table 26-1. ADC Register Summary

26.4.1 Control 1 Register (CTRL1)

Figure 26-2. Control 1 Register (CTRL1) Table 26-2. CTRL1 Field Descriptions

Table 26-1. ADC Register Summary (continued)

Table 26-2. CTRL1 Field Descriptions (continued)

26.4.2 Control 2 Register (CTRL2)

Figure 26-3. Control 2 Register (CTRL2) Under Sequential Scan Modes

26.4.2.1 CTRL2 Under Sequential Scan Modes

Table 26-2. CTRL1 Field Descriptions (continued)

26.4.2.2 CTRL2 Under Parallel Scan Modes

Table 26-3. CTRL2 Field Descriptions Under Sequential Scan Modes

Table 26-5. ADC Clock Frequency for Various Conversion Clock Sources

Table 26-4. CTRL2 Field Descriptions Under Parallel Scan Modes (continued)

26.4.3 Zero Crossing Control Register (ADZCC)

26.4.4 Channel List 1 and 2 Registers (ADLST1 and ADLST2)

Figure 26-6. Channel List 1 Register (ADLST1) Table 26-7. ADLST1 Field Descriptions

Figure 26-7. Channel List 2 Register (ADLST2)

26.4.5 Sample Disable Register (ADSDIS)

Table 26-8. ADLST2 Field Descriptions

Table 26-9. ADC Input Conversion for Sample Bits

26.4.6 Status Register (ADSTAT)

Table 26-11. ADSTAT Field Descriptions

26.4.7 Limit Status Register (ADLSTAT)

Figure 26-10. Limit Status Register (ADLSTAT) Table 26-12. ADLSTAT Field Descriptions

Table 26-11. ADSTAT Field Descriptions (continued)

26.4.8 Zero Crossing Status Register (ADZCSTAT)

26.4.9 Result Registers (ADRSLTn)

26.4.10 Low and High Limit Registers (ADLLMTn and ADHLMTn)

Figure 26-13. Low Limit Registers (ADLLMTn) Table 26-15. ADLLMTn Field Descriptions

Figure 26-14. High Limit Registers (ADHLMTn) Table 26-16. ADHLMTn Field Descriptions

26.4.11 Offset Registers (ADOFSn)

26.4.12 Power Control Register (POWER)

Page

Table 26-18. POWER Field Descriptions (continued)

26.4.13 Voltage Reference Register (CAL)

Figure 26-17. Voltage Reference Register (CAL) Table 26-19. CAL Field Descriptions

Table 26-18. POWER Field Descriptions (continued)

26.5 Functional Description

Figure 26-18. Sequential Mode Operation of the ADC

Figure 26-19. Parallel Mode Operation of the ADC

AN7

26.5.1 Input MUX Function

Figure 26-20. Input Select Mux

Table 26-20. Analog MUX Controls for Each Conversion Mode (continued)

26.5.2 ADC Sample Conversion

26.5.2.1 Single-Ended Samples

26.5.2.2 Differential Samples

26.5.3 ADC Data Processing

26.5.4 Sequential vs. Parallel Sampling

26.5.5 Scan Sequencing

26.5.6 Scan Configuration and Control

Table 26-21. ADC Scan Modes

26.5.7 Interrupt Sources

26.5.8 Power Management

26.5.8.1 Power Management Modes

26.5.8.2 Power Management Details

26.5.8.3 ADC STOP Mode of Operation

26.5.9 ADC Clock

26.5.9.1 General

26.5.9.2 Description of Clock Operation

26.5.9.3 ADC Clock Resynchronization at Start of Scan

Figure 26-27. ADC Clock Resynchronization for Non-Simultaneous Parallel Modes

26.5.10 Voltage Reference Pins VREFH and VREFL

Figure 26-28. ADC Voltage Reference Circuit

26.5.11 Suppl y Pins V

Freescale Semiconductor 27-1

Chapter 27 Pulse-Width Modulation (PWM) Module

27.1 Introduction

Figure 27-1. PWM Block Diagram

27.1.1 Overview

27.2 Memory Map/Register Definition

27.2.1 PWM Enable Register (PWME)

Figure 27-2. PWM Enable Register (PWME) Table 27-2. PWME Field Descriptions

27.2.2 PWM Polarity Register (PWMPOL)

27.2.3 PWM Clock Select Register (PWMCLK)

Figure 27-3. PWM Polarity Register (PWMPOL) Table 27-3. PWMPOL Field Descriptions

Table 27-2. PWME Field Descriptions (continued)

27.2.4 PWM Prescale Clock Select Register (PWMPRCLK)

Figure 27-4. PWM Clock Select Register (PWMCLK) Table 27-4. PWMCLK Field Descriptions

Figure 27-5. PWM Prescale Clock Select Register (PWMPRCLK)

27.2.5 PWM Center Align Enable Register (PWMCAE)

Table 27-5. PWMPRCLK Field Descriptions

Figure 27-6. PWM Center Align Enable Register (PWMCAE)

27.2.6 PWM Control Register (PWMCTL)

Table 27-6. PWMCAE Field Descriptions

Figure 27-7. PWM Control Register (PWMCTL) Table 27-7. PWMCTL Field Descriptions

27.2.7 PWM Scale A Register (PWMSCLA)

=

-----------------------------------------

Any value written to this register causes the scale counter to load the new scale value (PWMSCLA).

Eqn. 27-1

27.2.8 PWM Scale B Register (PWMSCLB)

27.2.9 PWM Channel Counter Registers (PWMCNTn)

27.2.10 PWM Channel Period Registers (PWMPERn)

27.2.11 PWM Channel Duty Registers (PWMDTYn)

27.2.12 PWM Shutdown Register (PWMSDN)

Table 27-12. PWMDTYn Field Descriptions

Figure 27-13. PWM Shutdown Register (PWMSDN) Table 27-13. PWMSDN Field Descriptions

27.3 Functional Description

27.3.1 PWM Clock Select

27-14 Freescale Semiconductor

Figure 27-14. PWM Clock Select Block Diagram

27.3.1.1 Prescaled Clock (A or B)

27.3.1.2 Scaled Clock (SA or SB)

27.3.1.3 Clock Select

27.3.2 PWM Channel Timers

27.3.2.1 PWM Enable

27.3.2.2 PWM Polarity

27.3.2.3 PWM Period and Duty

27.3.2.4 PWM Timer Counters

27.3.2.5 Left-Aligned Outputs

27.3.2.6 Center-Aligned Outputs

27.3.2.7 PWM 16-Bit Functions

Figure 27-20. PWM 16-Bit Mode

27.3.2.8 PWM Boundary Cases

Table 27-15. 16-bit Concatenation Mode Summary

Table 27-16. PWM Boundary Cases

Chapter 28 Debug Module

28.1 Introduction

28.1.1 Block Diagram

28.1.2 Overview

28.2 Signal Descriptions

28.3 Real-Time Trace Support

Table 28-3. Processor Status Encoding

28.3.1 Begin Execution of Taken Branch (PST = 0x5)

28.4 Memory Map/Register Definition

28.4.1 Shared Debug Resources

28.4.2 Configuration/Status Register (CSR)

Figure 28-3. Configuration/Status Register (CSR) Table 28-6. CSR Field Descriptions

Table 28-6. CSR Field Descriptions (continued)

28.4.3 BDM Address Attribute Register (BAAR)

28.4.4 Address Attribute Trigger Register (AATR)

Figure 28-4. BDM Address Attribute Register (BAAR) Table 28-7. BAAR Field Descriptions

Table 28-6. CSR Field Descriptions (continued)

Figure 28-5. Address Attribute Trigger Register (AATR) Table 28-8. AATR Field Descriptions

28.4.5 Trigger Definition Register (TDR)

Figure 28-6. Trigger Definition Register (TDR) Table 28-9. TDR Field Descriptions

Table 28-9. TDR Field Descriptions (continued)

28.4.6 Program Counter Breakpoint/Mask Registers (PBR03, PBMR)

Table 28-9. TDR Field Descriptions (continued)

Figure 28-7. PC Breakpoint Register (PBR0) Table 28-10. PBR0 Field Descriptions

Figure 28-8. PC Breakpoint Register n (PBRn) Table 28-11. PBRn Field Descriptions

28.4.7 Address Breakpoint Registers (ABLR, ABHR)

Figure 28-9. PC Breakpoint Mask Register (PBMR) Table 28-12. PBMR Field Descriptions

Figure 28-10. Address Breakpoint Registers (ABLR, ABHR,) Table 28-13. ABLR Field Description

Table 28-14. ABHR Field Description

28.4.8 Data Breakpoint and Mask Registers (DBR, DBMR)

Figure 28-11. Data Breakpoint Registers (DBR) Table 28-15. DBR Field Descriptions

Figure 28-12. Data Breakpoint Mask Registers (DBMR) Table 28-16. DBMR Field Descriptions

28.5 Background Debug Mode (BDM)

28.5.1 CPU Halt

28.5.2 BDM Serial Interface

28.5.2.1 Receive Packet Format

28.5.2.2 Transmit Packet Format

The basic transmit packet consists of 16 data bits and 1 reserved bit.

28.5.3 BDM Command Set

Table 28-18. Receive BDM Packet Field Description

Figure 28-15. Transmit BDM Packet Table 28-19. Transmit BDM Packet Field Description

Table 28-20. BDM Command Summary

28.5.3.1 ColdFire BDM Command Format

28.5.3.2 Command Sequence Diagrams

28.5.3.3 Command Set Descriptions

Page

Command/Result Formats:

Figure 28-23. READ Command Sequence

Figure 28-22.

Page

Page

Freescale Semiconductor 28-31

DUMP does not check for a valid address; it is a valid command only when

Figure 28-27. DUMP Command Sequence

Operand Data: None

Figure 28-26. DUMP Command/Result Formats

Page

Freescale Semiconductor 28-33

Figure 28-29.

Figure 28-31. GO Command Sequence

0x0 0xC 0x0 0x0

Figure 28-30. GO Command Format

Page

Page

Page

Page

Page

28.6 Real-Time Debug Support

28.6.1 Theory of Operation

Page

28.6.1.1 Emulator Mode

28.6.2 Concurrent BDM and Processor Operation

28.7 Processor Status, Debug Data Definition

28.7.1 User Instruction Set

Table 28-25. PST/DDATA Specification for User-Mode Instructions

Page

Table 28-25. PST/DDATA Specification for User-Mode Instructions (continued)

Table 28-26 shows the PST/DDATA specification for multiply-accumulate instructions.

Table 28-26. PST/DDATA Values for User-Mode Multiply-Accumulate Instructions

28.7.2 Supervisor Instruction Set

28.8 Freescale-Recommended BDM Pinout

Figure 28-44. Recommended BDM Connector

Freescale Semiconductor 29-1

Chapter 29 IEEE 1149.1 Test Access Port (JTAG)

29.1 Introduction

Figure 29-1. JTAG Block Diagram

29.1.1 Block Diagram

Figure 29-1 shows the block diagram of the JTAG module.

29.2 External Signal Description

29.2.1 JTAG Enable (JTAG_EN)

29.2.2 Test Clock Input (TCLK)

29.2.3 Test Mode Select/Breakpoint (TMS/BKPT)

29.2.4 Test Data Input/Development Serial Input (TDI/DSI)

29.2.5 Test Reset/Development Serial Clock (TRST/DSCLK)

29.2.6 Test Data Output/Development Serial Output (TDO/DSO)

29.3 Memory Map/Register Definition

29.3.1 Instruction Shift Register (IR)

29.3.2 IDCODE Register

29.3.3 Bypass Register

29.3.4 JTAG_CFM_CLKDIV Register

29.3.5 TEST_CTRL Register

29.3.6 Boundary Scan Register

29.4 Functional Description

29.4.1 JTAG Module

29.4.2 TAP Controller

Figure 29-4. TAP Controller State Machine Flow

29.4.3 JTAG Instructions

Table 29-5 describes public and private instructions.

Table 29-5. JTAG Instructions

29.4.3.1 IDCODE Instruction

29.4.3.2 SAMPLE/PRELOAD Instruction

29.4.3.3 EXTEST Instruction

29.4.3.4 TEST_LEAKAGE Instruction

29.4.3.5 ENABLE_TEST_CTRL Instruction

29.4.3.6 HIGHZ Instruction

29.4.3.7 LOCKOUT_RECOVERY Instruction

29.4.3.8 CLAMP Instruction

29.5 Initialization/Application Information

29.5.1 Restrictions

29.5.2 Nonscan Chain Operation

Appendix A Register Memory Map Quick Reference

Table A-2. Module Memory Map Overview

Table A-3. Register Memory Map

Table A-2. Module Memory Map Overview (continued)

Page

Page

Page

Page

Page

Page

Page

Page

Page

Page

Page

Page

Page

Page

Page

Page

Page

Appendix B Revision History

B.1 Changes between Rev. 1 and Rev. 2

Table 1. MCF52211RM Rev. 1 to Rev. 2 Changes

B.2 Changes between Rev. 0 and Rev. 1

Table 2. MCF52211RM Rev. 0 to Rev. 1 Changes