5.3 Host Commands

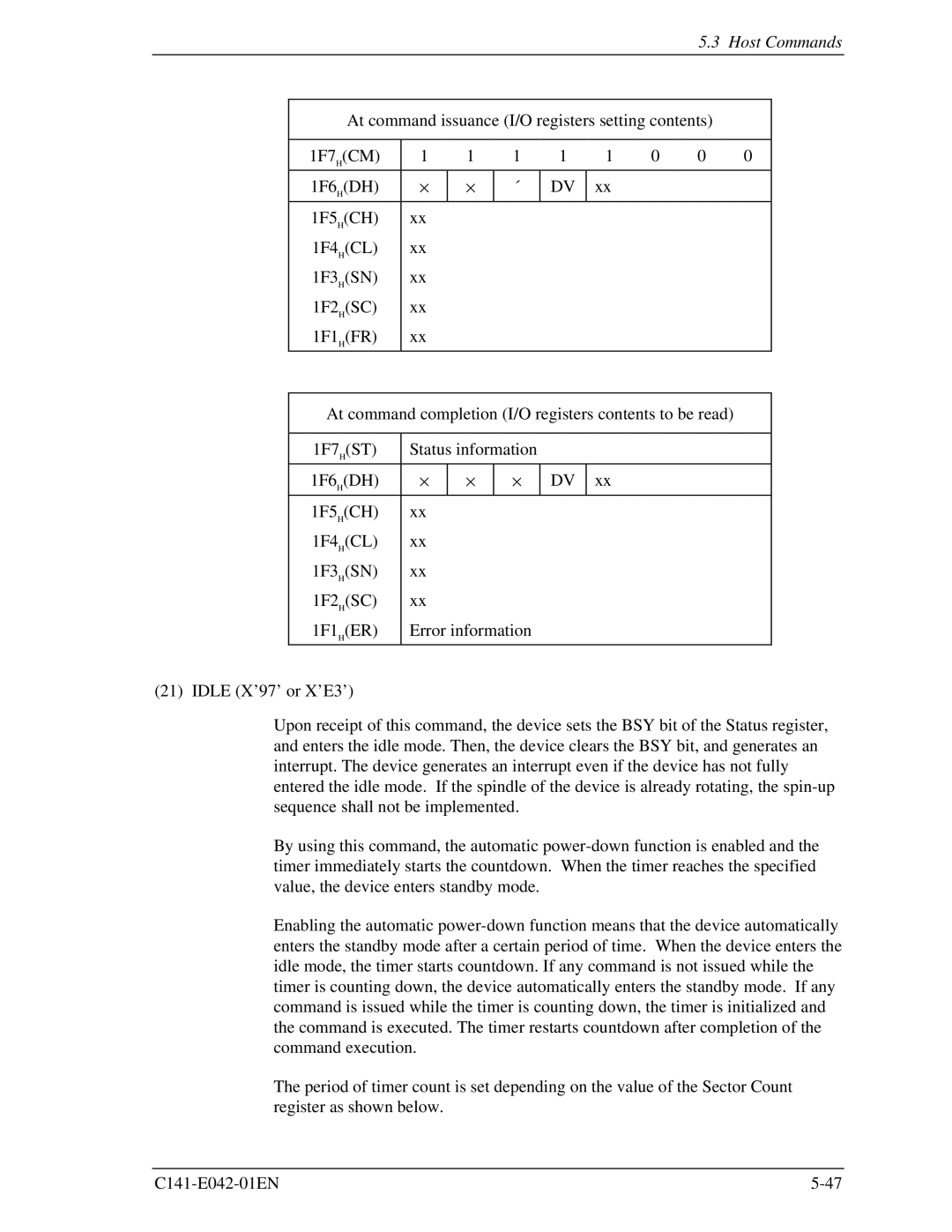

At command issuance (I/O registers setting contents)

1F7H(CM) | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 |

1F6H(DH) | × | × | ´ | DV | xx |

|

|

|

|

|

|

|

|

|

|

|

|

1F5H(CH) | xx |

|

|

|

|

|

|

|

1F4H(CL) | xx |

|

|

|

|

|

|

|

1F3H(SN) | xx |

|

|

|

|

|

|

|

1F2H(SC) | xx |

|

|

|

|

|

|

|

1F1H(FR) | xx |

|

|

|

|

|

|

|

At command completion (I/O registers contents to be read)

1F7H(ST) | Status information |

|

| ||

1F6H(DH) | × | × | × | DV | xx |

|

|

|

|

|

|

1F5H(CH) | xx |

|

|

|

|

1F4H(CL) | xx |

|

|

|

|

1F3H(SN) | xx |

|

|

|

|

1F2H(SC) | xx |

|

|

|

|

1F1H(ER) | Error information |

|

| ||

(21) IDLE (X’97’ or X’E3’)

Upon receipt of this command, the device sets the BSY bit of the Status register, and enters the idle mode. Then, the device clears the BSY bit, and generates an interrupt. The device generates an interrupt even if the device has not fully entered the idle mode. If the spindle of the device is already rotating, the

By using this command, the automatic

Enabling the automatic

The period of timer count is set depending on the value of the Sector Count register as shown below.