|

|

|

|

|

|

|

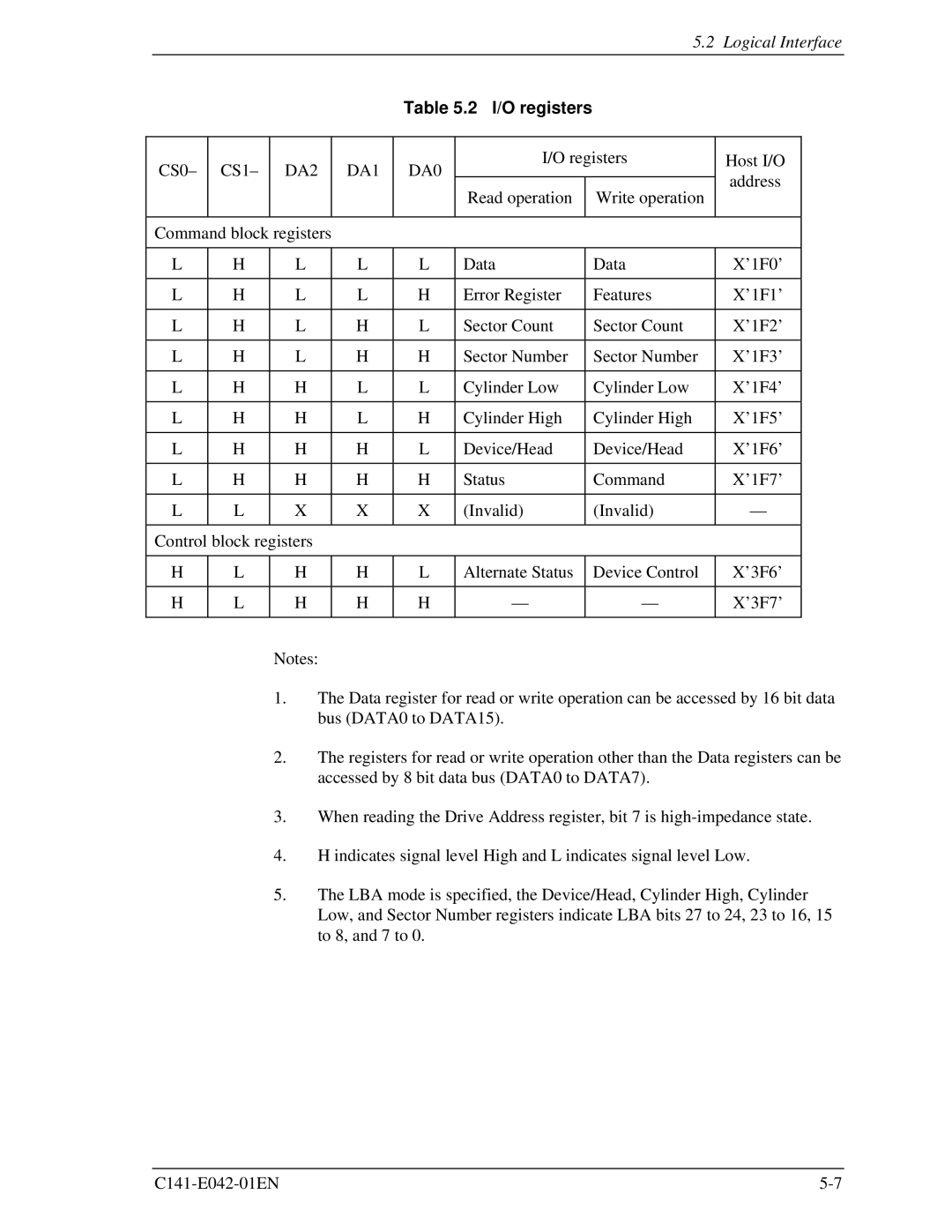

| 5.2 Logical Interface | |||

|

|

|

|

| Table 5.2 I/O registers |

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

| |

| CS0– | CS1– | DA2 | DA1 | DA0 | I/O registers |

| Host I/O |

| ||

|

|

|

|

| address |

| |||||

|

|

|

|

|

| Read operation |

| Write operation |

|

| |

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

| Command block registers |

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

| |

| L | H | L | L | L | Data |

| Data |

| X’1F0’ |

|

|

|

|

|

|

|

|

|

|

|

|

|

| L | H | L | L | H | Error Register |

| Features |

| X’1F1’ |

|

|

|

|

|

|

|

|

|

|

|

|

|

| L | H | L | H | L | Sector Count |

| Sector Count |

| X’1F2’ |

|

|

|

|

|

|

|

|

|

|

|

|

|

| L | H | L | H | H | Sector Number |

| Sector Number |

| X’1F3’ |

|

|

|

|

|

|

|

|

|

|

|

|

|

| L | H | H | L | L | Cylinder Low |

| Cylinder Low |

| X’1F4’ |

|

|

|

|

|

|

|

|

|

|

|

|

|

| L | H | H | L | H | Cylinder High |

| Cylinder High |

| X’1F5’ |

|

|

|

|

|

|

|

|

|

|

|

|

|

| L | H | H | H | L | Device/Head |

| Device/Head |

| X’1F6’ |

|

|

|

|

|

|

|

|

|

|

|

|

|

| L | H | H | H | H | Status |

| Command |

| X’1F7’ |

|

|

|

|

|

|

|

|

|

|

|

|

|

| L | L | X | X | X | (Invalid) |

| (Invalid) |

| — |

|

|

|

|

|

|

|

|

|

|

|

|

|

| Control block registers |

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

| |

| H | L | H | H | L | Alternate Status |

| Device Control |

| X’3F6’ |

|

|

|

|

|

|

|

|

|

|

|

|

|

| H | L | H | H | H | — |

| — |

| X’3F7’ |

|

|

|

|

|

|

|

|

|

|

|

|

|

Notes:

1.The Data register for read or write operation can be accessed by 16 bit data bus (DATA0 to DATA15).

2.The registers for read or write operation other than the Data registers can be accessed by 8 bit data bus (DATA0 to DATA7).

3.When reading the Drive Address register, bit 7 is

4.H indicates signal level High and L indicates signal level Low.

5.The LBA mode is specified, the Device/Head, Cylinder High, Cylinder Low, and Sector Number registers indicate LBA bits 27 to 24, 23 to 16, 15 to 8, and 7 to 0.