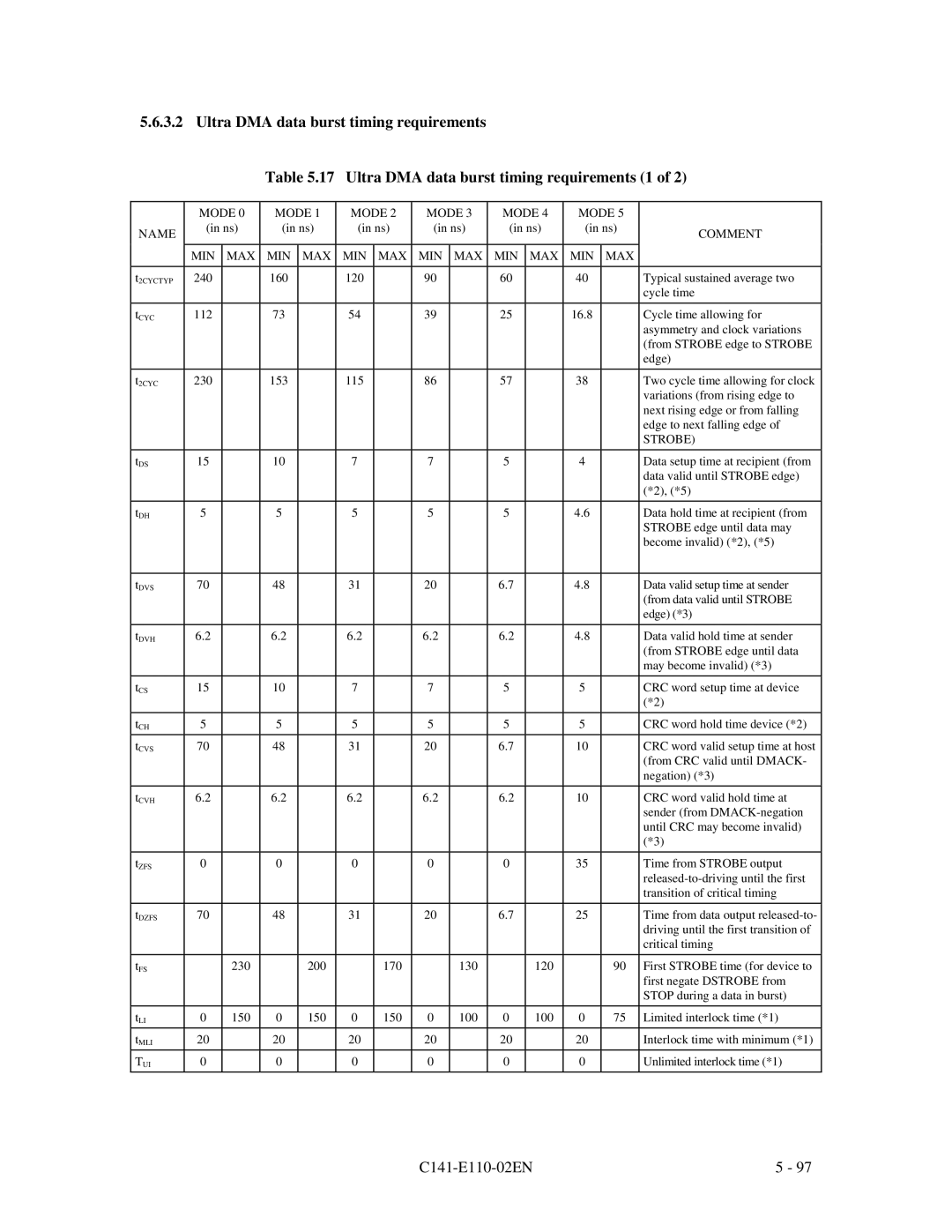

5.6.3.2 Ultra DMA data burst timing requirements

Table 5.17 Ultra DMA data burst timing requirements (1 of 2)

| MODE 0 | MODE 1 | MODE 2 | MODE 3 | MODE 4 | MODE 5 |

| ||||||

NAME | (in ns) | (in ns) | (in ns) | (in ns) | (in ns) | (in ns) | COMMENT | ||||||

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| MIN | MAX | MIN | MAX | MIN | MAX | MIN | MAX | MIN | MAX | MIN | MAX |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t2CYCTYP | 240 |

| 160 |

| 120 |

| 90 |

| 60 |

| 40 |

| Typical sustained average two |

|

|

|

|

|

|

|

|

|

|

|

|

| cycle time |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tCYC | 112 |

| 73 |

| 54 |

| 39 |

| 25 |

| 16.8 |

| Cycle time allowing for |

|

|

|

|

|

|

|

|

|

|

|

|

| asymmetry and clock variations |

|

|

|

|

|

|

|

|

|

|

|

|

| (from STROBE edge to STROBE |

|

|

|

|

|

|

|

|

|

|

|

|

| edge) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t2CYC | 230 |

| 153 |

| 115 |

| 86 |

| 57 |

| 38 |

| Two cycle time allowing for clock |

|

|

|

|

|

|

|

|

|

|

|

|

| variations (from rising edge to |

|

|

|

|

|

|

|

|

|

|

|

|

| next rising edge or from falling |

|

|

|

|

|

|

|

|

|

|

|

|

| edge to next falling edge of |

|

|

|

|

|

|

|

|

|

|

|

|

| STROBE) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tDS | 15 |

| 10 |

| 7 |

| 7 |

| 5 |

| 4 |

| Data setup time at recipient (from |

|

|

|

|

|

|

|

|

|

|

|

|

| data valid until STROBE edge) |

|

|

|

|

|

|

|

|

|

|

|

|

| (*2), (*5) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tDH | 5 |

| 5 |

| 5 |

| 5 |

| 5 |

| 4.6 |

| Data hold time at recipient (from |

|

|

|

|

|

|

|

|

|

|

|

|

| STROBE edge until data may |

|

|

|

|

|

|

|

|

|

|

|

|

| become invalid) (*2), (*5) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tDVS | 70 |

| 48 |

| 31 |

| 20 |

| 6.7 |

| 4.8 |

| Data valid setup time at sender |

|

|

|

|

|

|

|

|

|

|

|

|

| (from data valid until STROBE |

|

|

|

|

|

|

|

|

|

|

|

|

| edge) (*3) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tDVH | 6.2 |

| 6.2 |

| 6.2 |

| 6.2 |

| 6.2 |

| 4.8 |

| Data valid hold time at sender |

|

|

|

|

|

|

|

|

|

|

|

|

| (from STROBE edge until data |

|

|

|

|

|

|

|

|

|

|

|

|

| may become invalid) (*3) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tCS | 15 |

| 10 |

| 7 |

| 7 |

| 5 |

| 5 |

| CRC word setup time at device |

|

|

|

|

|

|

|

|

|

|

|

|

| (*2) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tCH | 5 |

| 5 |

| 5 |

| 5 |

| 5 |

| 5 |

| CRC word hold time device (*2) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tCVS | 70 |

| 48 |

| 31 |

| 20 |

| 6.7 |

| 10 |

| CRC word valid setup time at host |

|

|

|

|

|

|

|

|

|

|

|

|

| (from CRC valid until DMACK- |

|

|

|

|

|

|

|

|

|

|

|

|

| negation) (*3) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tCVH | 6.2 |

| 6.2 |

| 6.2 |

| 6.2 |

| 6.2 |

| 10 |

| CRC word valid hold time at |

|

|

|

|

|

|

|

|

|

|

|

|

| sender (from |

|

|

|

|

|

|

|

|

|

|

|

|

| until CRC may become invalid) |

|

|

|

|

|

|

|

|

|

|

|

|

| (*3) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tZFS | 0 |

| 0 |

| 0 |

| 0 |

| 0 |

| 35 |

| Time from STROBE output |

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

| transition of critical timing |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tDZFS | 70 |

| 48 |

| 31 |

| 20 |

| 6.7 |

| 25 |

| Time from data output |

|

|

|

|

|

|

|

|

|

|

|

|

| driving until the first transition of |

|

|

|

|

|

|

|

|

|

|

|

|

| critical timing |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tFS |

| 230 |

| 200 |

| 170 |

| 130 |

| 120 |

| 90 | First STROBE time (for device to |

|

|

|

|

|

|

|

|

|

|

|

|

| first negate DSTROBE from |

|

|

|

|

|

|

|

|

|

|

|

|

| STOP during a data in burst) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tLI | 0 | 150 | 0 | 150 | 0 | 150 | 0 | 100 | 0 | 100 | 0 | 75 | Limited interlock time (*1) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tMLI | 20 |

| 20 |

| 20 |

| 20 |

| 20 |

| 20 |

| Interlock time with minimum (*1) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TUI | 0 |

| 0 |

| 0 |

| 0 |

| 0 |

| 0 |

| Unlimited interlock time (*1) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 5 - 97 |