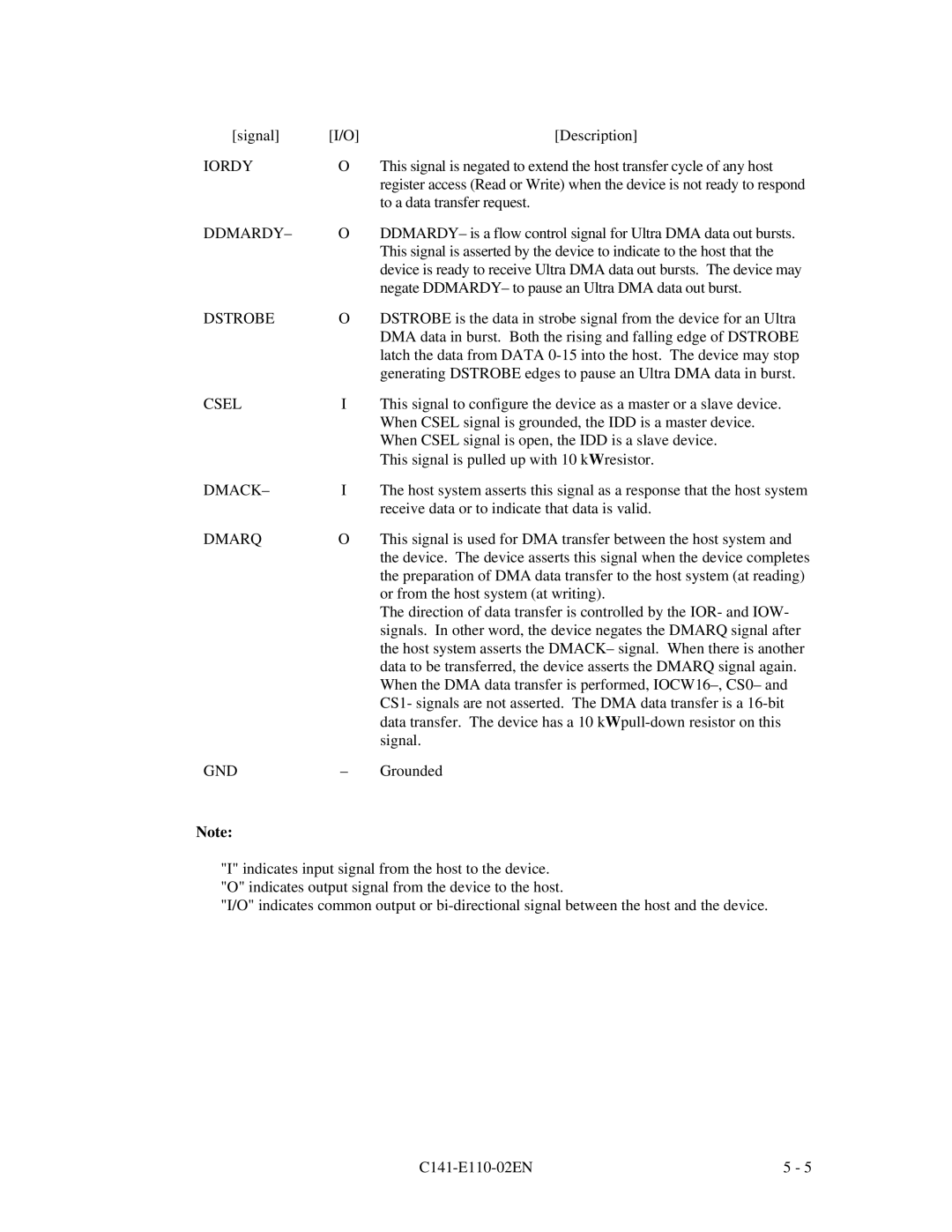

[signal] | [I/O] | [Description] |

IORDY | O | This signal is negated to extend the host transfer cycle of any host |

|

| register access (Read or Write) when the device is not ready to respond |

|

| to a data transfer request. |

DDMARDY– | O | DDMARDY– is a flow control signal for Ultra DMA data out bursts. |

|

| This signal is asserted by the device to indicate to the host that the |

|

| device is ready to receive Ultra DMA data out bursts. The device may |

|

| negate DDMARDY– to pause an Ultra DMA data out burst. |

DSTROBE | O | DSTROBE is the data in strobe signal from the device for an Ultra |

|

| DMA data in burst. Both the rising and falling edge of DSTROBE |

|

| latch the data from DATA |

|

| generating DSTROBE edges to pause an Ultra DMA data in burst. |

CSEL | I | This signal to configure the device as a master or a slave device. |

|

| When CSEL signal is grounded, the IDD is a master device. |

|

| When CSEL signal is open, the IDD is a slave device. |

|

| This signal is pulled up with 10 kΩ resistor. |

DMACK– | I | The host system asserts this signal as a response that the host system |

|

| receive data or to indicate that data is valid. |

DMARQ | O | This signal is used for DMA transfer between the host system and |

|

| the device. The device asserts this signal when the device completes |

|

| the preparation of DMA data transfer to the host system (at reading) |

|

| or from the host system (at writing). |

|

| The direction of data transfer is controlled by the IOR- and IOW- |

|

| signals. In other word, the device negates the DMARQ signal after |

|

| the host system asserts the DMACK– signal. When there is another |

|

| data to be transferred, the device asserts the DMARQ signal again. |

|

| When the DMA data transfer is performed, |

|

| CS1- signals are not asserted. The DMA data transfer is a |

|

| data transfer. The device has a 10 kΩ |

|

| signal. |

GND | – | Grounded |

Note:

"I" indicates input signal from the host to the device. "O" indicates output signal from the device to the host.

"I/O" indicates common output or

| 5 - 5 |