If device 1 is present:

∙Both devices shall execute

∙The device 0 waits for up to 5 seconds until device 1 asserts the PDIAG- signal.

∙If the device 1 does not assert the PDIAG- signal but indicates an error, the device 0 shall append X'80' to its own diagnostic status.

∙The device 0 clears the BSY bit of the Status register and generates an interrupt. (The device 1 does not generate an interrupt.)

∙A diagnostic status of the device 0 is read by the host system. When a diagnostic failure of the device 1 is detected, the host system can read a status of the device 1 by setting the DV bit (selecting the device 1).

When device 1 is not present:

∙The device 0 posts only the results of its own

∙The device 0 clears the BSY bit of the Status register, and generates an interrupt.

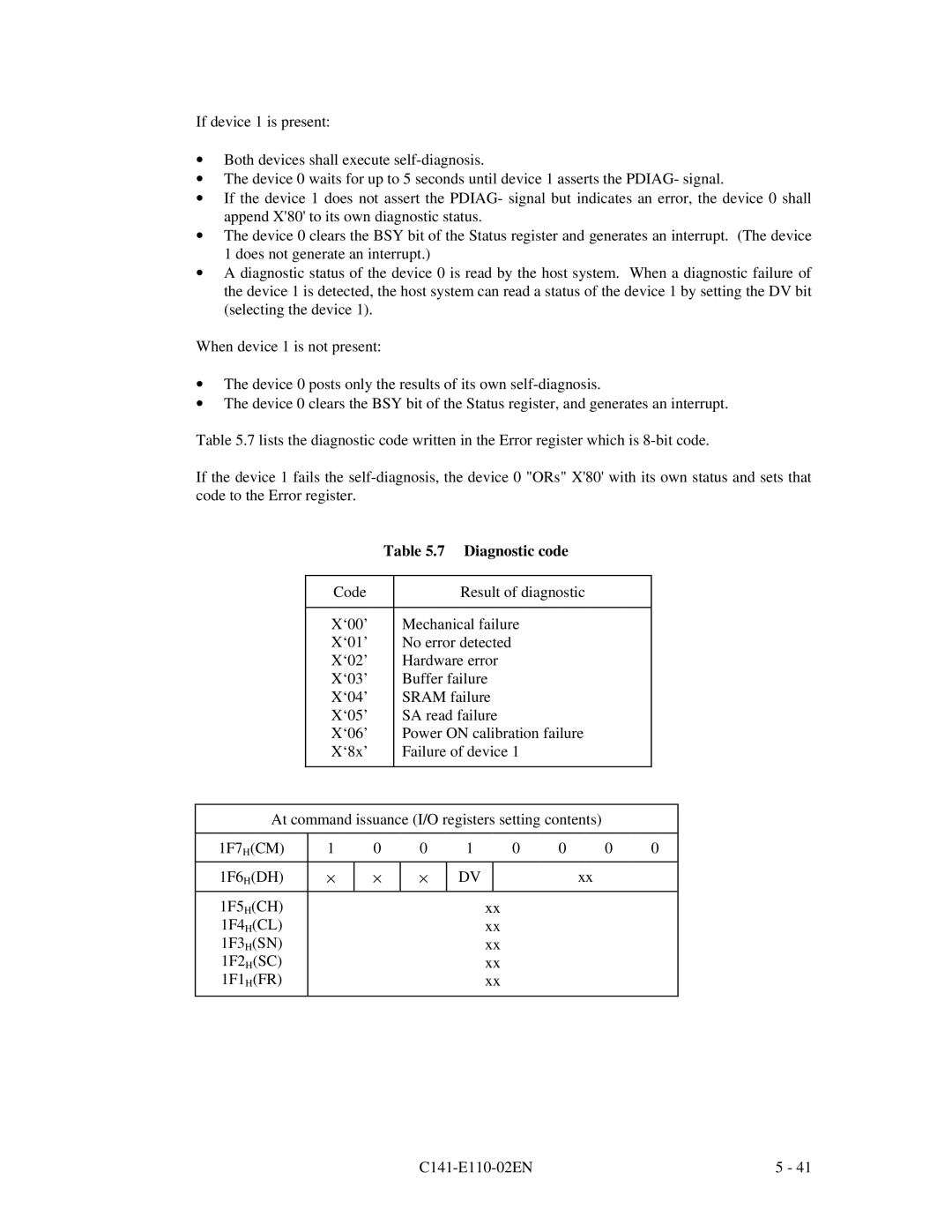

Table 5.7 lists the diagnostic code written in the Error register which is

If the device 1 fails the

| Table 5.7 Diagnostic code | |

|

|

|

Code |

| Result of diagnostic |

|

|

|

X‘00’ |

| Mechanical failure |

X‘01’ |

| No error detected |

X‘02’ |

| Hardware error |

X‘03’ |

| Buffer failure |

X‘04’ |

| SRAM failure |

X‘05’ |

| SA read failure |

X‘06’ |

| Power ON calibration failure |

X‘8x’ |

| Failure of device 1 |

|

|

|

At command issuance (I/O registers setting contents)

1F7H(CM) | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | |

|

|

|

|

|

|

|

|

|

|

1F6H(DH) | × | × | × | DV |

|

|

| xx |

|

|

|

|

|

|

|

|

|

|

|

1F5H(CH) |

|

|

|

| xx |

|

|

| |

1F4H(CL) |

|

|

|

| xx |

|

|

| |

1F3H(SN) |

|

|

|

| xx |

|

|

| |

1F2H(SC) |

|

|

|

| xx |

|

|

| |

1F1H(FR) |

|

|

|

| xx |

|

|

| |

|

|

|

|

|

|

|

|

|

|

| 5 - 41 |