|

|

| Console I/F (RS232C) | |

| Himalaya 2.0 |

|

| |

Switch | 40.0 MHz |

| ||

|

| |||

Flash ROM |

| MCU |

|

|

ARM7TDMI |

|

| ||

64K × 16 bits |

|

| ||

|

|

|

| |

|

| RDC |

|

|

ATA |

|

| ||

|

|

|

| |

Series Termination |

| HDC |

|

|

| SH7661 |

|

| |

I/F |

| Head IC | SVC | |

|

| |||

|

|

| SR1756 | HA13627 |

– PIO |

|

|

|

|

– Multiword DMA |

|

|

|

|

– Ultra DMA | Buffer | Bandwidth = 160.0 MB/s | R/W | SPM/VCM |

– Ultra DMA |

|

| control | |

|

|

| ||

| Data Buffer |

|

| |

| 256K × 16 bits |

|

| |

|

| Option |

|

|

| (1024K × 16 bits) |

|

| |

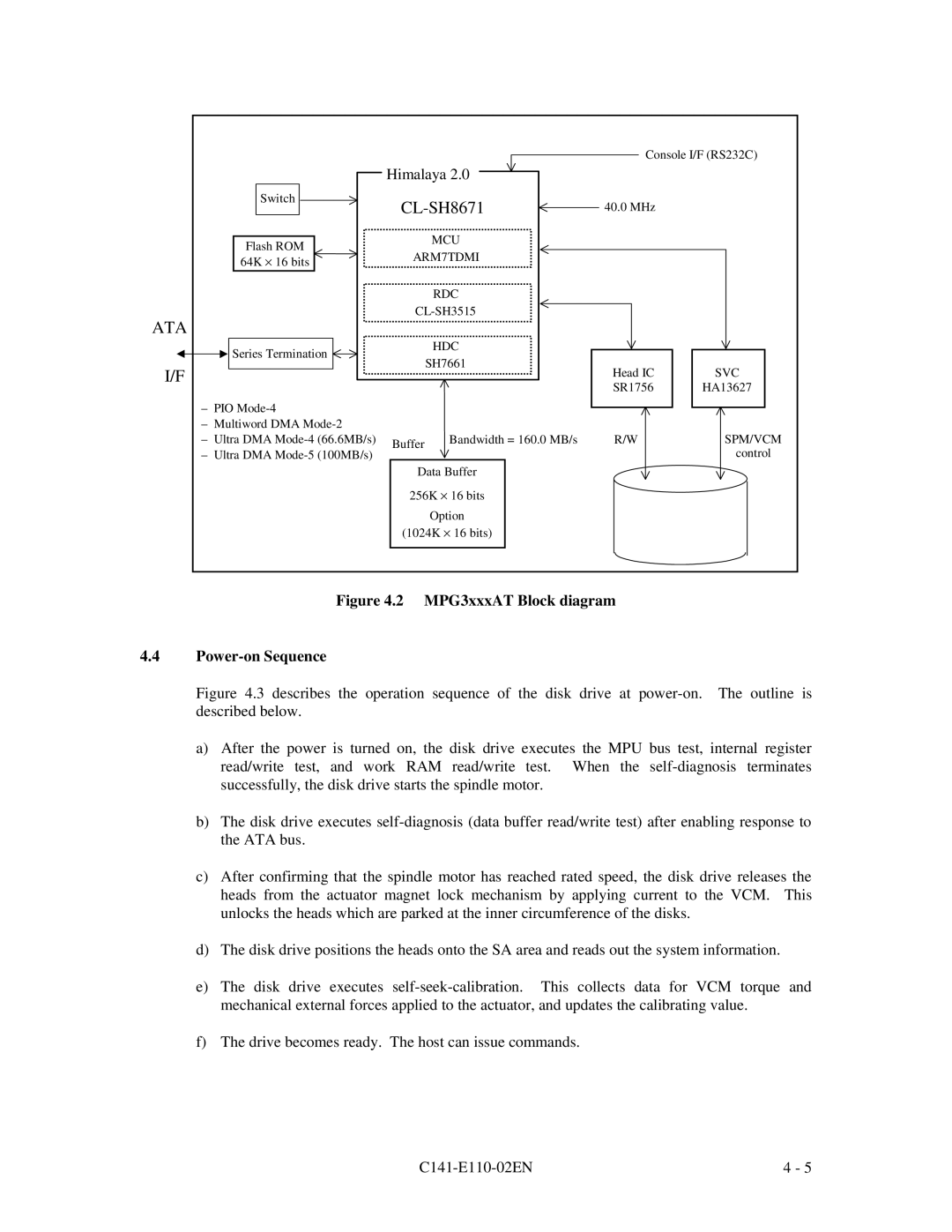

Figure 4.2 MPG3xxxAT Block diagram

4.4Power-on Sequence

Figure 4.3 describes the operation sequence of the disk drive at power-on. The outline is described below.

a)After the power is turned on, the disk drive executes the MPU bus test, internal register read/write test, and work RAM read/write test. When the self-diagnosis terminates successfully, the disk drive starts the spindle motor.

b)The disk drive executes self-diagnosis (data buffer read/write test) after enabling response to the ATA bus.

c)After confirming that the spindle motor has reached rated speed, the disk drive releases the heads from the actuator magnet lock mechanism by applying current to the VCM. This unlocks the heads which are parked at the inner circumference of the disks.

d)The disk drive positions the heads onto the SA area and reads out the system information.

e)The disk drive executes self-seek-calibration. This collects data for VCM torque and mechanical external forces applied to the actuator, and updates the calibrating value.

f)The drive becomes ready. The host can issue commands.

| 4 - 5 |