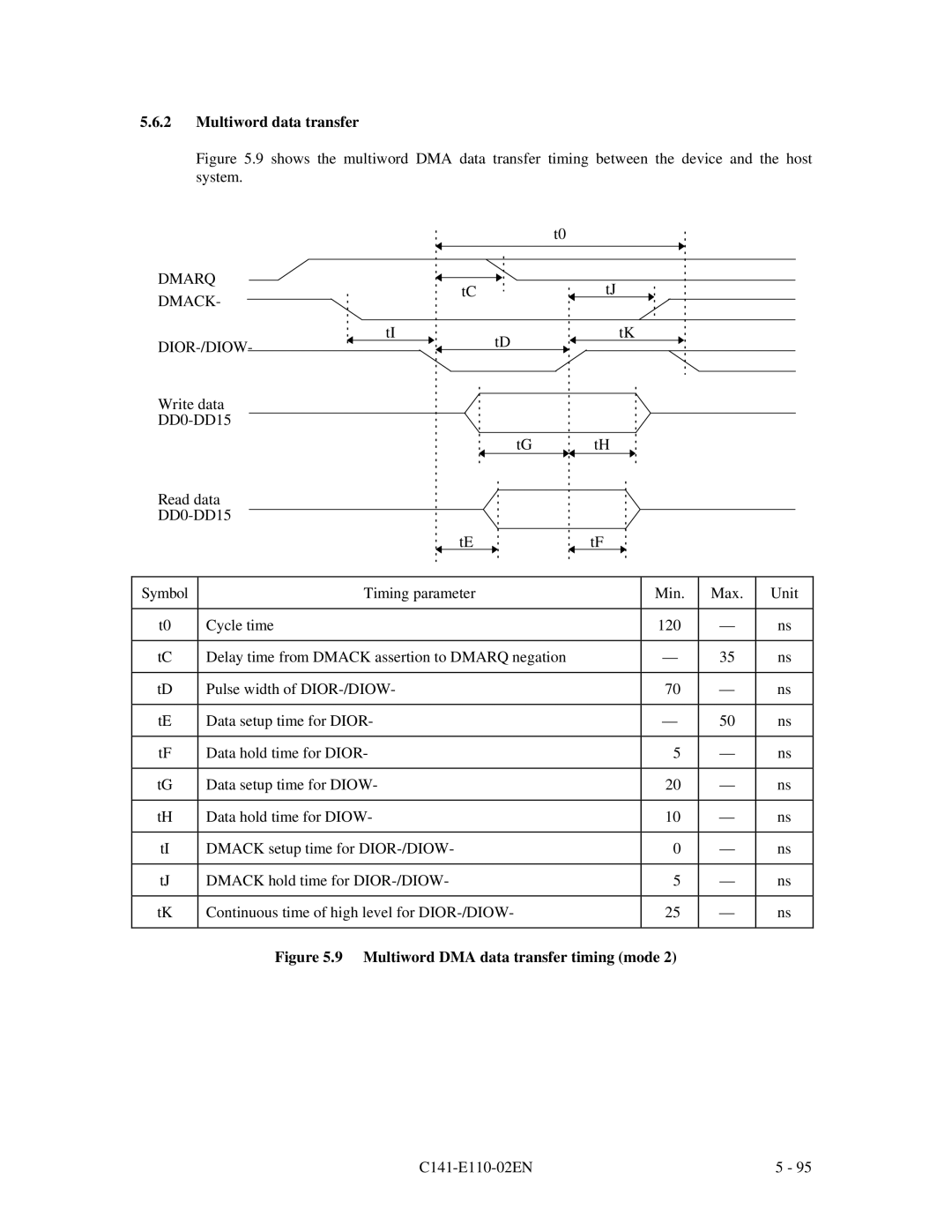

5.6.2Multiword data transfer

Figure 5.9 shows the multiword DMA data transfer timing between the device and the host system.

|

|

|

|

|

|

| t0 |

|

|

|

|

|

|

|

| |

DMARQ |

|

|

|

|

| tJ |

|

| ||||||||

tC |

|

|

|

|

|

| ||||||||||

|

|

|

|

|

|

|

|

|

| |||||||

DMACK- |

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

| tI |

|

| tD | tK |

|

|

| |||||||

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

Write data |

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

| tG | tH |

|

| ||||||

Read data |

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

| tE |

|

|

|

| tF |

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

Symbol |

| Timing parameter |

|

|

|

|

|

|

|

| Min. | Max. | Unit | |||

|

|

|

|

|

|

|

|

|

| |||||||

t0 | Cycle time |

|

|

|

|

| 120 | — | ns | |||||||

|

|

|

|

|

|

|

|

| ||||||||

tC | Delay time from DMACK assertion to DMARQ negation |

|

|

|

| — | 35 | ns | ||||||||

|

|

|

|

|

|

|

|

|

| |||||||

tD | Pulse width of |

|

|

|

|

| 70 | — | ns | |||||||

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

tE | Data setup time for DIOR- |

|

|

|

|

|

|

|

| — | 50 | ns | ||||

|

|

|

|

|

|

|

|

|

| |||||||

tF | Data hold time for DIOR- |

|

|

|

|

| 5 | — | ns | |||||||

|

|

|

|

|

|

|

|

|

| |||||||

tG | Data setup time for DIOW- |

|

|

|

|

| 20 | — | ns | |||||||

|

|

|

|

|

|

|

|

|

| |||||||

tH | Data hold time for DIOW- |

|

|

|

|

| 10 | — | ns | |||||||

|

|

|

|

|

|

|

|

|

| |||||||

tI | DMACK setup time for |

|

|

|

|

| 0 | — | ns | |||||||

|

|

|

|

|

|

|

|

|

| |||||||

tJ | DMACK hold time for |

|

|

|

|

| 5 | — | ns | |||||||

|

|

|

|

|

| |||||||||||

tK | Continuous time of high level for |

| 25 | — | ns | |||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Figure 5.9 Multiword DMA data transfer timing (mode 2)

| 5 - 95 |