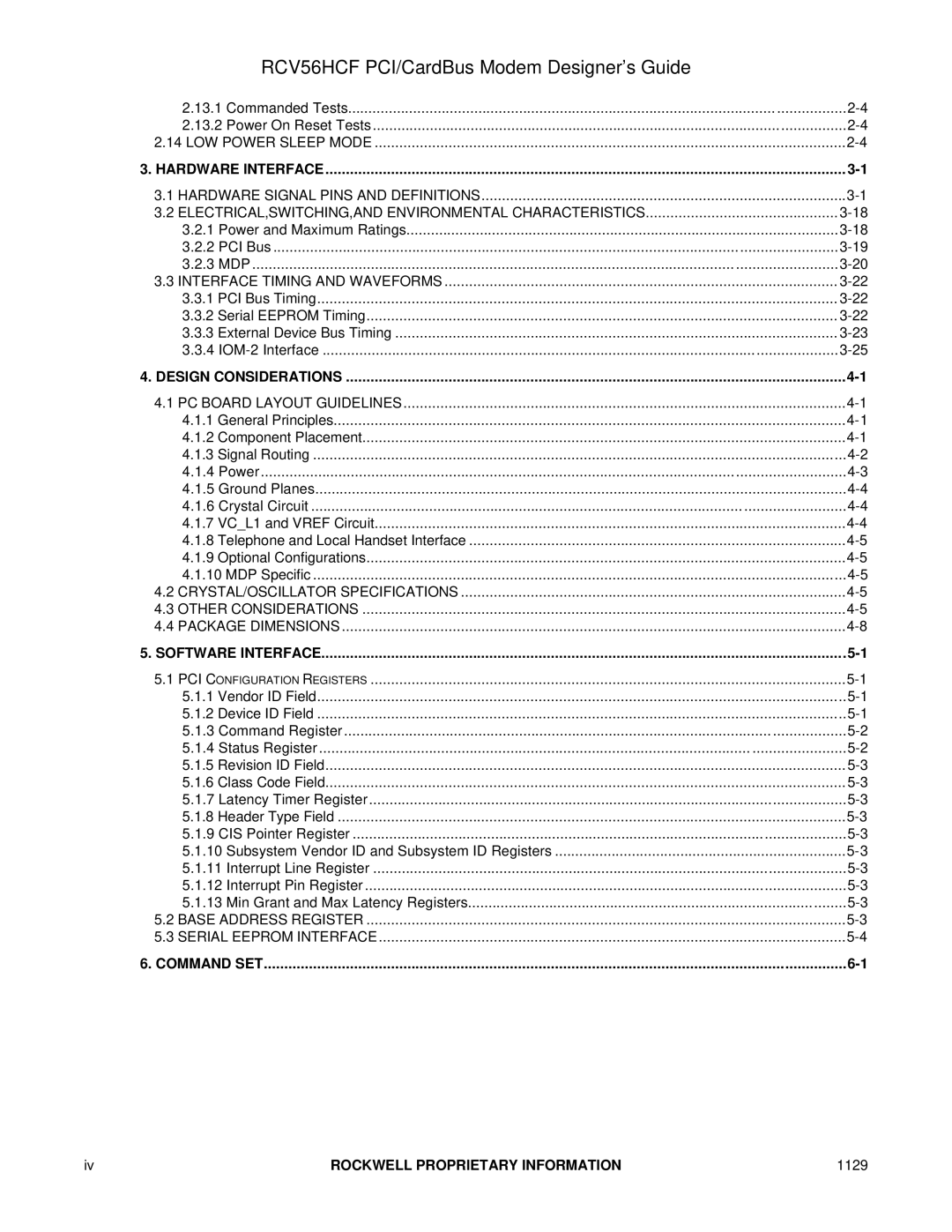

RCV56HCF PCI/CardBus Modem Designer’s Guide

2.13.1 Commanded Tests | |

2.13.2 Power On Reset Tests | |

2.14 LOW POWER SLEEP MODE | |

3. HARDWARE INTERFACE | |

3.1 HARDWARE SIGNAL PINS AND DEFINITIONS | |

3.2 ELECTRICAL,SWITCHING,AND ENVIRONMENTAL CHARACTERISTICS | |

3.2.1 Power and Maximum Ratings | |

3.2.2 PCI Bus | |

3.2.3 MDP | |

3.3 INTERFACE TIMING AND WAVEFORMS | |

3.3.1 PCI Bus Timing | |

3.3.2 Serial EEPROM Timing | |

3.3.3 External Device Bus Timing | |

3.3.4 | |

4. DESIGN CONSIDERATIONS | |

4.1 PC BOARD LAYOUT GUIDELINES | |

4.1.1 General Principles | |

4.1.2 Component Placement | |

4.1.3 Signal Routing | |

4.1.4 Power | |

4.1.5 Ground Planes | |

4.1.6 Crystal Circuit | |

4.1.7 VC_L1 and VREF Circuit | |

4.1.8 Telephone and Local Handset Interface | |

4.1.9 Optional Configurations | |

4.1.10 MDP Specific | |

4.2 CRYSTAL/OSCILLATOR SPECIFICATIONS | |

4.3 OTHER CONSIDERATIONS | |

4.4 PACKAGE DIMENSIONS | |

5. SOFTWARE INTERFACE | |

5.1 PCI CONFIGURATION REGISTERS | |

5.1.1 Vendor ID Field | |

5.1.2 Device ID Field | |

5.1.3 Command Register | |

5.1.4 Status Register | |

5.1.5 Revision ID Field | |

5.1.6 Class Code Field | |

5.1.7 Latency Timer Register | |

5.1.8 Header Type Field | |

5.1.9 CIS Pointer Register | |

5.1.10 Subsystem Vendor ID and Subsystem ID Registers | |

5.1.11 Interrupt Line Register | |

5.1.12 Interrupt Pin Register | |

5.1.13 Min Grant and Max Latency Registers | |

5.2 BASE ADDRESS REGISTER | |

5.3 SERIAL EEPROM INTERFACE | |

6. COMMAND SET |

iv | ROCKWELL PROPRIETARY INFORMATION | 1129 |