EM78P447N

4.5.2 The Status of RST, T, and P of STATUS Register

A RESET condition is initiated by one of the following events:

1.A

2.A

3.Watchdog timer

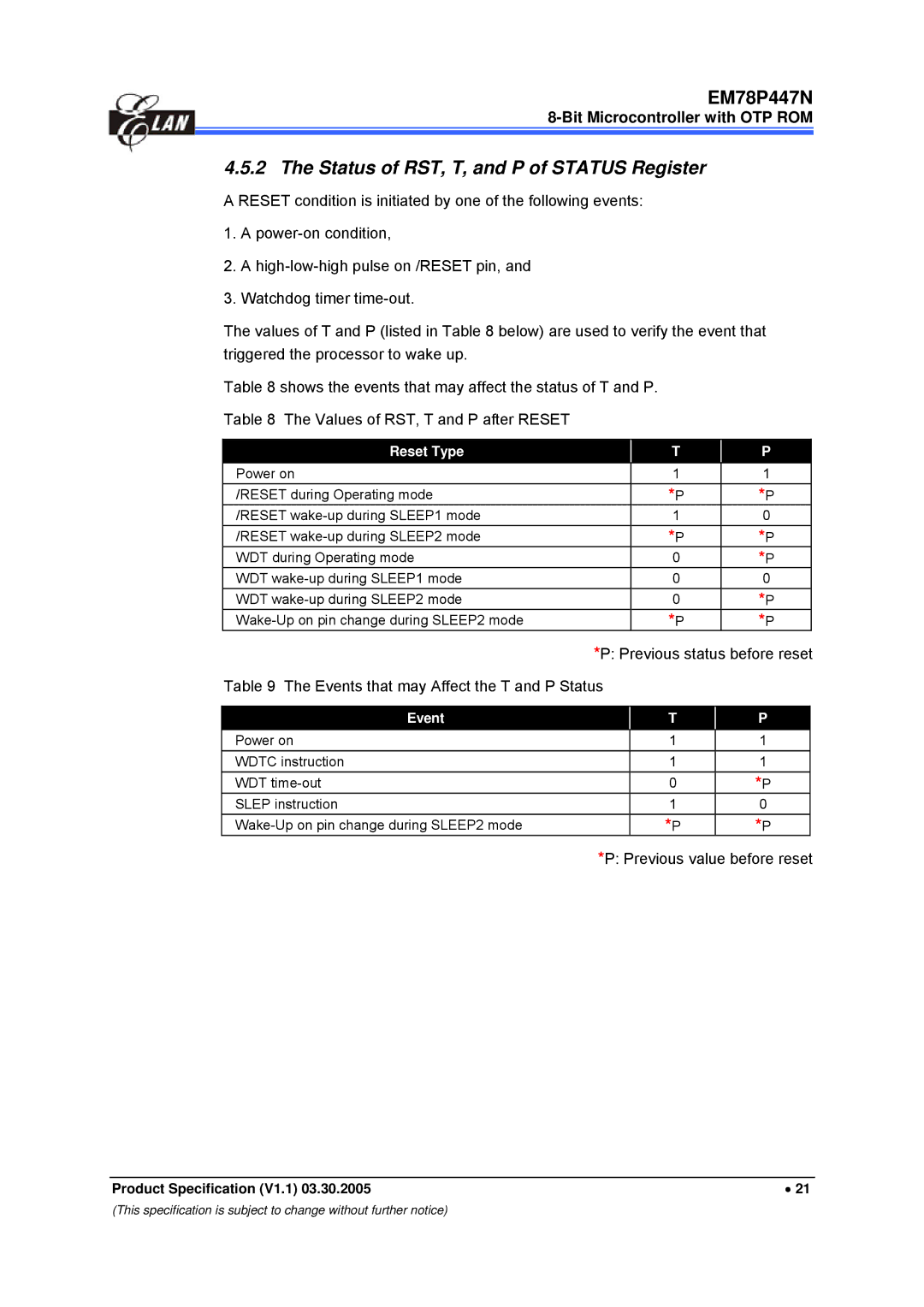

The values of T and P (listed in Table 8 below) are used to verify the event that triggered the processor to wake up.

Table 8 shows the events that may affect the status of T and P.

Table 8 The Values of RST, T and P after RESET

| Reset Type |

|

| T |

|

| P |

|

| |

| Power on |

|

| 1 |

|

|

| 1 |

|

|

| /RESET during Operating mode |

|

| *P |

|

| *P |

| ||

| /RESET |

|

| 1 |

|

|

| 0 |

|

|

| /RESET |

|

| *P |

|

| *P |

| ||

| WDT during Operating mode |

|

| 0 |

|

|

| *P |

| |

| WDT |

|

| 0 |

|

|

| 0 |

|

|

| WDT |

|

| 0 |

|

|

| *P |

| |

|

|

| *P |

|

| *P |

| |||

|

| *P: Previous status before reset | ||||||||

Table 9 The Events that may Affect the T and P Status |

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

| Event |

|

| T |

|

|

| P |

|

|

| Power on |

|

| 1 |

| 1 |

|

| ||

| WDTC instruction |

|

| 1 |

| 1 |

|

| ||

| WDT |

|

| 0 |

|

|

| *P |

| |

| SLEP instruction |

|

| 1 |

| 0 |

|

| ||

|

|

| *P |

|

|

| *P |

| ||

*P: Previous value before reset

Product Specification (V1.1) 03.30.2005 | • 21 |

(This specification is subject to change without further notice)