MAX12527 | | | 1 LSB = 4/3 x (VREFP - VREFN) / 4096 |

| 2/3 x (VREFP - VREFN) | | | 2/3 x (VREFP - VREFN) |

| 0x7FF | | | | | |

COMPLEMENT OUTPUT CODE (LSB) | 0x7FE | | | | | |

0x7FD | | | | | |

0x001 | | | | | |

0x000 | | | | | |

0xFFF | | | | | |

| | | | | |

| - | | | | | | |

| TWO'S | 0x803 | | | | | |

| 0x802 | | | | | |

| | | | | | |

| | 0x801 | | | | | |

| | 0x800 | | | | | |

| | -2047 | -2045 | -1 | 0 | +1 | +2045 +2047 |

| | | DIFFERENTIAL INPUT VOLTAGE (LSB) |

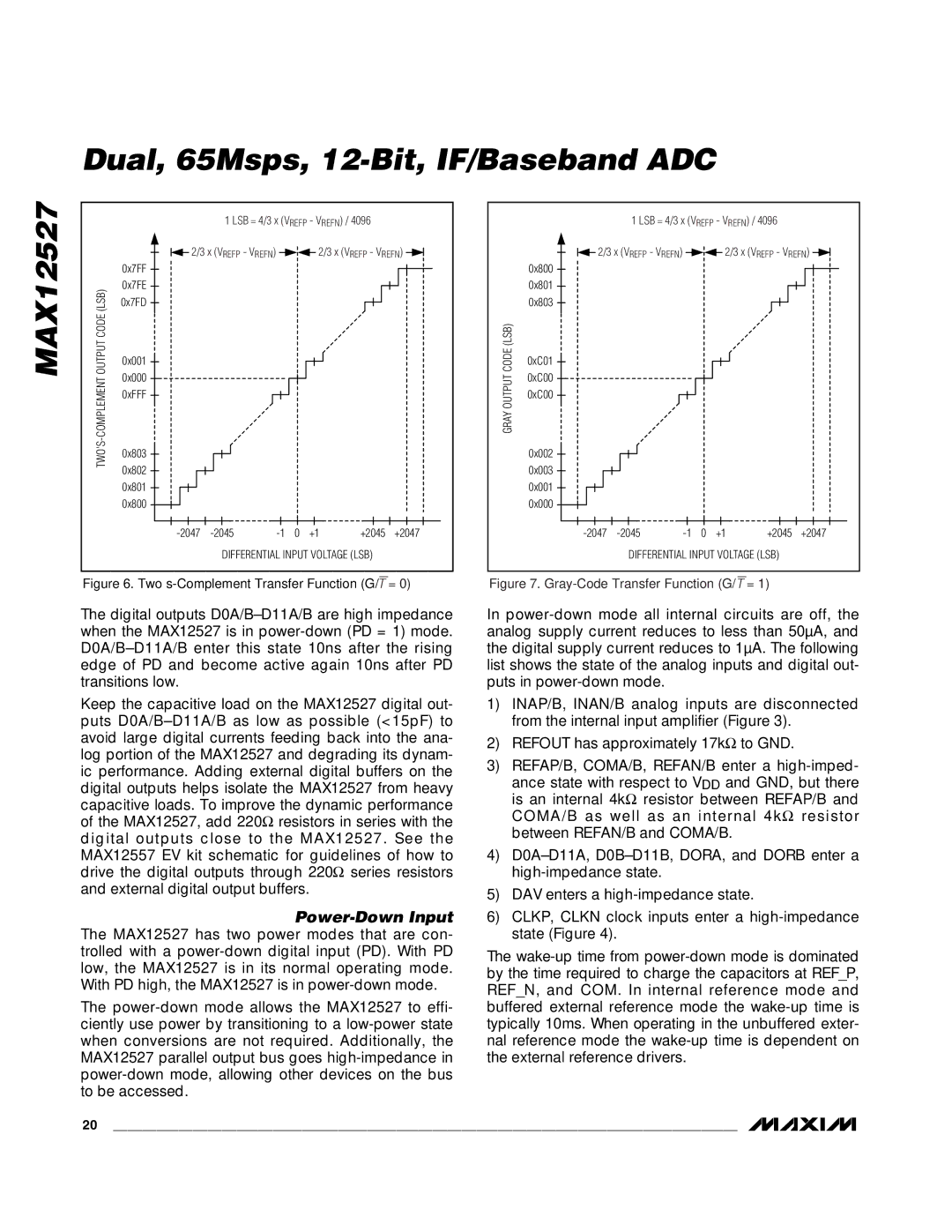

| Figure 6. Two’s-Complement Transfer Function (G/T = 0) |

The digital outputs D0A/B–D11A/B are high impedance when the MAX12527 is in power-down (PD = 1) mode. D0A/B–D11A/B enter this state 10ns after the rising edge of PD and become active again 10ns after PD transitions low.

Keep the capacitive load on the MAX12527 digital out- puts D0A/B–D11A/B as low as possible (<15pF) to avoid large digital currents feeding back into the ana- log portion of the MAX12527 and degrading its dynam- ic performance. Adding external digital buffers on the digital outputs helps isolate the MAX12527 from heavy capacitive loads. To improve the dynamic performance of the MAX12527, add 220Ω resistors in series with the digital outputs close to the MAX12527. See the MAX12557 EV kit schematic for guidelines of how to drive the digital outputs through 220Ω series resistors and external digital output buffers.

Power-Down Input

The MAX12527 has two power modes that are con- trolled with a power-down digital input (PD). With PD low, the MAX12527 is in its normal operating mode. With PD high, the MAX12527 is in power-down mode.

The power-down mode allows the MAX12527 to effi- ciently use power by transitioning to a low-power state when conversions are not required. Additionally, the MAX12527 parallel output bus goes high-impedance in power-down mode, allowing other devices on the bus to be accessed.

| | 1 LSB = 4/3 x (VREFP - VREFN) / 4096 | |

| 2/3 x (VREFP - VREFN) | | | 2/3 x (VREFP - VREFN) |

| 0x800 | | | | | | |

| 0x801 | | | | | | |

| 0x803 | | | | | | |

(LSB) | | | | | | | |

CODE | 0xC01 | | | | | | |

0xC00 | | | | | | |

GRAY OUTPUT | | | | | | |

0xC00 | | | | | | |

| | | | | | |

| 0x002 | | | | | | |

| 0x003 | | | | | | |

| 0x001 | | | | | | |

| 0x000 | | | | | | |

| -2047 | -2045 | -1 | 0 | +1 | +2045 | +2047 |

| | DIFFERENTIAL INPUT VOLTAGE (LSB) | |

Figure 7. Gray-Code Transfer Function (G/T = 1) | |

In power-down mode all internal circuits are off, the analog supply current reduces to less than 50µA, and the digital supply current reduces to 1µA. The following list shows the state of the analog inputs and digital out- puts in power-down mode.

1)INAP/B, INAN/B analog inputs are disconnected from the internal input amplifier (Figure 3).

2)REFOUT has approximately 17kΩ to GND.

3)REFAP/B, COMA/B, REFAN/B enter a high-imped-

ance state with respect to VDD and GND, but there is an internal 4kΩ resistor between REFAP/B and COMA/B as well as an internal 4kΩ resistor between REFAN/B and COMA/B.

4)D0A–D11A, D0B–D11B, DORA, and DORB enter a high-impedance state.

5)DAV enters a high-impedance state.

6)CLKP, CLKN clock inputs enter a high-impedance state (Figure 4).

The wake-up time from power-down mode is dominated by the time required to charge the capacitors at REF_P, REF_N, and COM. In internal reference mode and buffered external reference mode the wake-up time is typically 10ms. When operating in the unbuffered exter- nal reference mode the wake-up time is dependent on the external reference drivers.