MAX12527

Dual, 65Msps, 12-Bit, IF/Baseband ADC

|

|

|

| Pin Description (continued) | |

|

|

|

|

| |

PIN | NAME |

| FUNCTION | ||

|

|

|

|

| |

|

| Shared Reference Digital Input. | |||

|

| SHREF = VDD: Shared reference enabled. | |||

66 | SHREF | SHREF = GND: Shared reference disabled. | |||

When sharing the reference, externally connect REFAP and REFBP together to ensure that VREFAP | |||||

|

| ||||

|

| equals VREFBP. Similarly, when sharing the reference, externally connect REFAN to REFBN together to | |||

|

| ensure that VREFAN = VREFBN. | |||

|

| Internal Reference Voltage Output. The REFOUT output voltage is 2.048V and REFOUT can deliver 1mA. | |||

|

| For internal reference operation, connect REFOUT directly to REFIN or use a resistive divider from | |||

67 | REFOUT | REFOUT to set the voltage at REFIN. Bypass REFOUT to GND with a ≥0.1µF capacitor. | |||

|

| For external reference operation, REFOUT is not required and must be bypassed to GND with a ≥0.1µF | |||

|

| capacitor. | |||

|

| ||||

|

| For internal reference and buffered external reference operation, apply a 0.7V to 2.3V DC reference | |||

68 | REFIN | voltage to REFIN. Bypass REFIN to GND with a 4.7µF capacitor. Within its specified operating voltage, | |||

REFIN has a >50MΩ input impedance, and the differential reference voltage (VREF_P - VREF_N) is | |||||

|

| ||||

|

| generated from REFIN. For unbuffered external reference operation, connect REFIN to GND. In this | |||

|

| mode REF_P, REF_N, and COM_ are | |||

— | EP | Exposed Paddle. EP is internally connected to GND. Externally connect EP to GND to achieve specified | |||

dynamic performance. | |||||

|

| ||||

|

|

|

|

| |

|

| + | Σ | x2 | |

|

|

| |||

MAX12527 |

|

|

| ||

|

| − |

| ||

|

|

|

| ||

| FLASH | DAC |

|

| |

| ADC |

|

| ||

|

|

|

| ||

IN_P |

|

|

| STAGE 10 | |

STAGE 1 | STAGE 2 | STAGE 9 | |||

END OF PIPELINE | |||||

IN_N |

|

|

| ||

|

|

|

| ||

| DIGITAL ERROR CORRECTION |

| |||

|

|

| D0_ THROUGH D11_ | ||

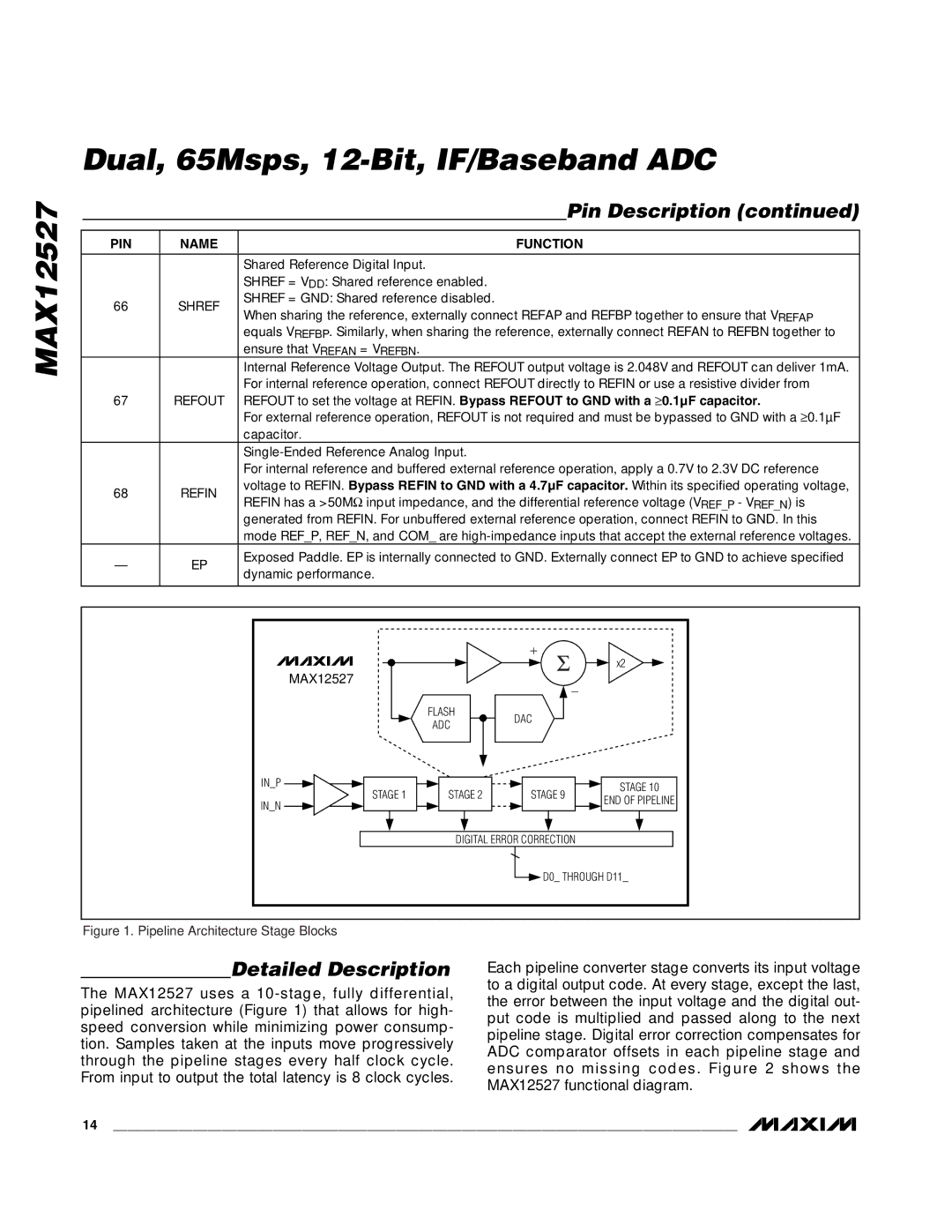

Figure 1. Pipeline Architecture—Stage Blocks

Detailed Description

The MAX12527 uses a

Each pipeline converter stage converts its input voltage to a digital output code. At every stage, except the last, the error between the input voltage and the digital out- put code is multiplied and passed along to the next pipeline stage. Digital error correction compensates for ADC comparator offsets in each pipeline stage and ensures no missing codes. Figure 2 shows the MAX12527 functional diagram.

14 ______________________________________________________________________________________