Dual, 65Msps, 12-Bit, IF/Baseband ADC

MAX12527

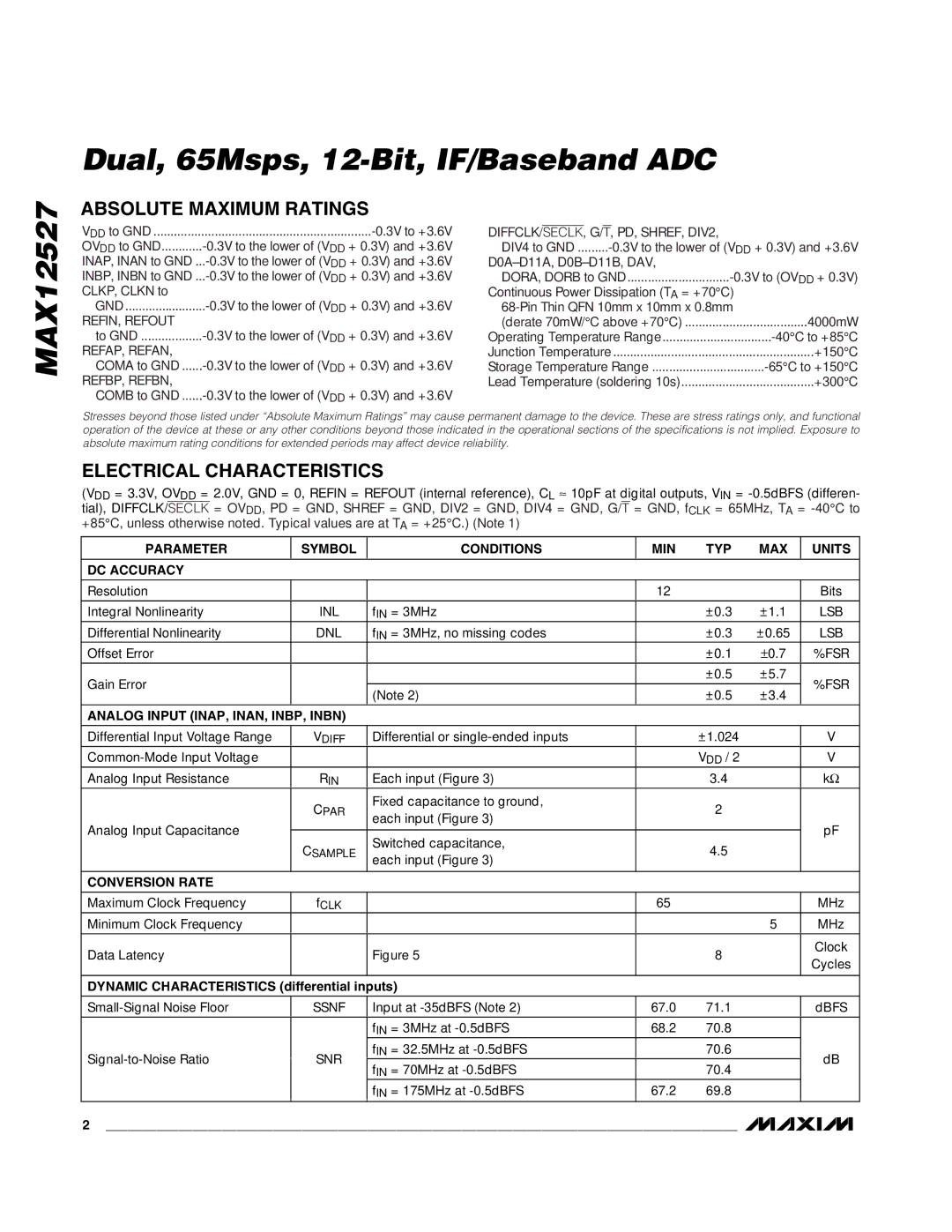

ABSOLUTE MAXIMUM RATINGS

VDD to GND | |

OVDD to GND | |

INAP, INAN to GND ... | |

INBP, INBN to GND ... | |

CLKP, CLKN........................to | |

GND | |

REFIN, REFOUT | |

to GND | |

REFAP, REFAN, | |

COMA to GND | |

REFBP, REFBN, | |

COMB to GND |

DIFFCLK/SECLK, G/T, PD, SHREF, DIV2, |

| |

DIV4 to GND | ||

DORA, DORB to GND | ||

Continuous Power Dissipation (TA = +70°C) |

|

| |

(derate 70mW/°C above +70°C) | 4000mW |

Operating Temperature Range | |

Junction Temperature | +150°C |

Storage Temperature Range | |

Lead Temperature (soldering 10s) | +300°C |

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

ELECTRICAL CHARACTERISTICS

(VDD = 3.3V, OVDD = 2.0V, GND = 0, REFIN = REFOUT (internal reference), CL ≈ 10pF at digital outputs, VIN =

+85°C, unless otherwise noted. Typical values are at TA = +25°C.) (Note 1)

PARAMETER | SYMBOL | CONDITIONS | MIN | TYP | MAX | UNITS |

|

|

|

|

|

|

|

DC ACCURACY |

|

|

|

|

|

|

|

|

|

|

|

|

|

Resolution |

|

| 12 |

|

| Bits |

Integral Nonlinearity | INL | fIN = 3MHz |

| ±0.3 | ±1.1 | LSB |

Differential Nonlinearity | DNL | fIN = 3MHz, no missing codes |

| ±0.3 | ±0.65 | LSB |

Offset Error |

|

|

| ±0.1 | ±0.7 | %FSR |

Gain Error |

|

|

| ±0.5 | ±5.7 | %FSR |

|

|

|

|

| ||

| (Note 2) |

| ±0.5 | ±3.4 | ||

|

|

|

| |||

ANALOG INPUT (INAP, INAN, INBP, INBN) |

|

|

|

|

| |

Differential Input Voltage Range | VDIFF | Differential or |

| ±1.024 |

| V |

|

|

| VDD / 2 |

| V | |

Analog Input Resistance | RIN | Each input (Figure 3) |

| 3.4 |

| kΩ |

| CPAR | Fixed capacitance to ground, |

| 2 |

|

|

| each input (Figure 3) |

|

|

| ||

Analog Input Capacitance |

|

|

|

| pF | |

|

|

|

|

| ||

CSAMPLE | Switched capacitance, |

| 4.5 |

| ||

|

|

|

| |||

| each input (Figure 3) |

|

|

| ||

|

|

|

|

|

| |

|

|

|

|

|

|

|

CONVERSION RATE |

|

|

|

|

|

|

Maximum Clock Frequency | fCLK |

| 65 |

|

| MHz |

Minimum Clock Frequency |

|

|

|

| 5 | MHz |

|

|

|

|

|

|

|

Data Latency |

| Figure 5 |

| 8 |

| Clock |

|

|

| Cycles | |||

|

|

|

|

|

| |

|

|

|

|

|

|

|

DYNAMIC CHARACTERISTICS (differential inputs) |

|

|

|

| ||

SSNF | Input at | 67.0 | 71.1 |

| dBFS | |

|

|

|

|

|

|

|

|

| fIN = 3MHz at | 68.2 | 70.8 |

|

|

SNR | fIN = 32.5MHz at |

| 70.6 |

| dB | |

fIN = 70MHz at |

| 70.4 |

| |||

|

|

|

|

| ||

|

| fIN = 175MHz at | 67.2 | 69.8 |

|

|

2 _______________________________________________________________________________________