Contents

Features

General Description

Applications

Ordering Information

Parameter Symbol Conditions MIN TYP MAX Units DC Accuracy

Dynamic Characteristics differential inputs

Analog Input INAP, INAN, INBP, Inbn

Conversion Rate

Parameter Symbol Conditions MIN TYP MAX Units

Internal Reference Refout

Interchannel Characteristics

Vcom

Parameter Symbol Conditions MIN TYP

Clock Inputs CLKP, Clkn

Digital Inputs DIFFCLK/ SECLK, G/ T, PD, DIV2, DIV4

Digital Outputs D0A-D11A, D0B-D11B, DORA, DORB, DAV

Power Requirements

D0A-D11A, Dora

Ovdd

DIFFCLK/SECLK = GND

Typical Operating Characteristics

Timing Characteristics Figure

FFT Plot 16,384-POINT Data Record

FFT Plot 32,768-POINT Data Record

MAX12527

THD, Sfdr vs. Clock Speed fIN = 70MHz, AIN = -0.5dBFS

FIN = 70MHz, AIN = -0.5dBFS

FCLK = 65.00352MHz, fIN = 175MHz

THD, Sfdr vs. Clock Duty Cycle FIN = 70MHz, AIN = -0.5dBFS

SNR, Sinad vs. Temperature fIN = 175MHz, AIN = -0.5dBFS

PIN Name Function

Pin Description

Same side of the PC board

D0B

D1B

D2B

D3B

Detailed Description

Shref

Refout

Refin

Functional Diagram

Reference Configurations

Reference Mode

Analog Inputs and Input Track-and-Hold T/H Amplifier

Reference Output

Clock Duty-Cycle Equalizer

Clock Input and Clock Control Lines

System Timing Requirements

DIV4 DIV2 Function

Equivalent Binary

D11A-D0A

DOR

D11A-D0A D11B-D0B CODE10

Power-Down Input

Vrefp Vrefn

Binary-to-Gray and Gray-to-Binary Code Conversion

Single-Ended AC-Coupled Input Signal

Using Transformer Coupling

Applications Information

Buffered External Reference Drives Multiple ADCs

Unbuffered External Reference Drives Multiple ADCs

Grounding, Bypassing, and Board Layout

MAX12527

Parameter Definitions

Aperture Delay

Full-Power Bandwidth

Overdrive Recovery Time

Total Harmonic Distortion THD

Gain Matching

Pin Configuration

Offset Matching

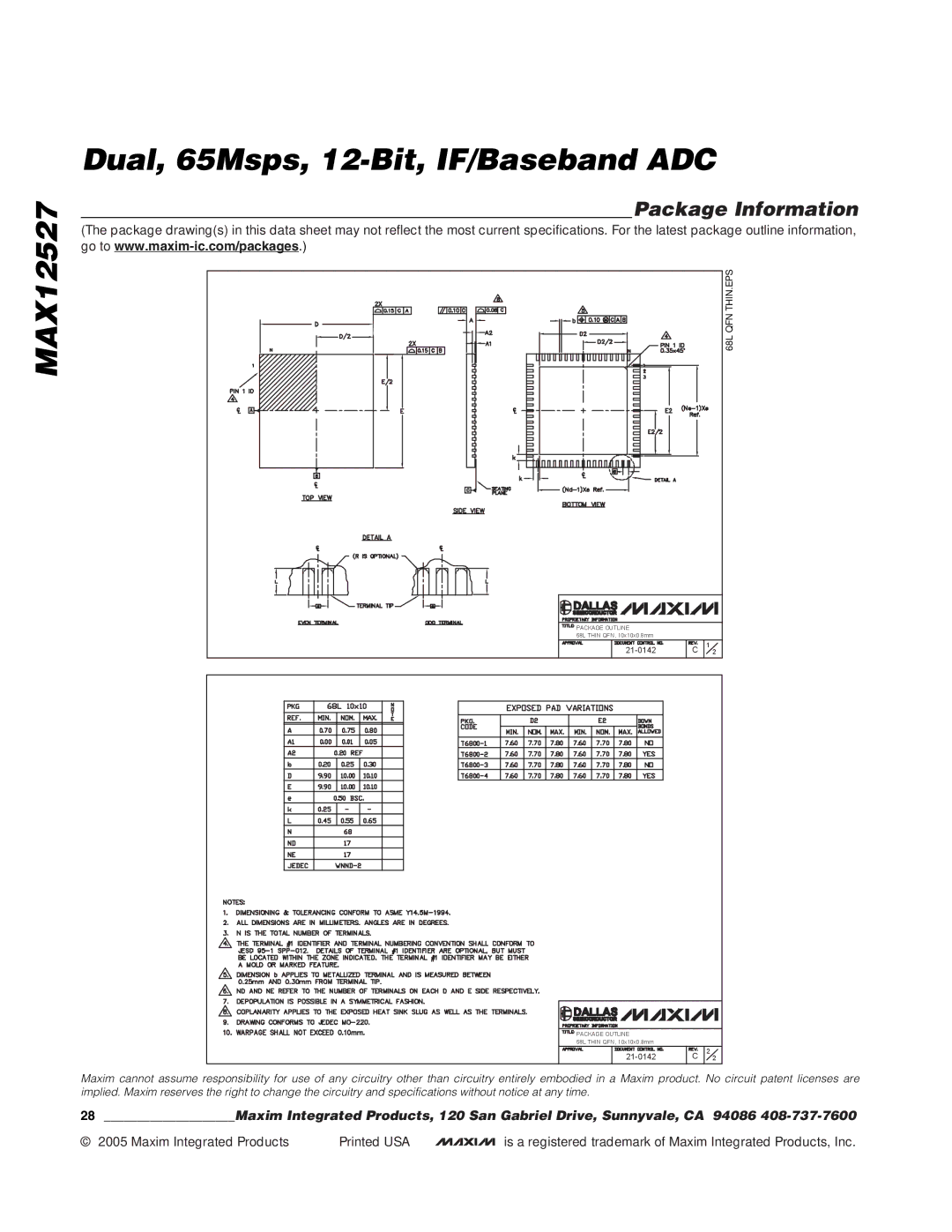

Package Information

68L QFN THIN.EPS