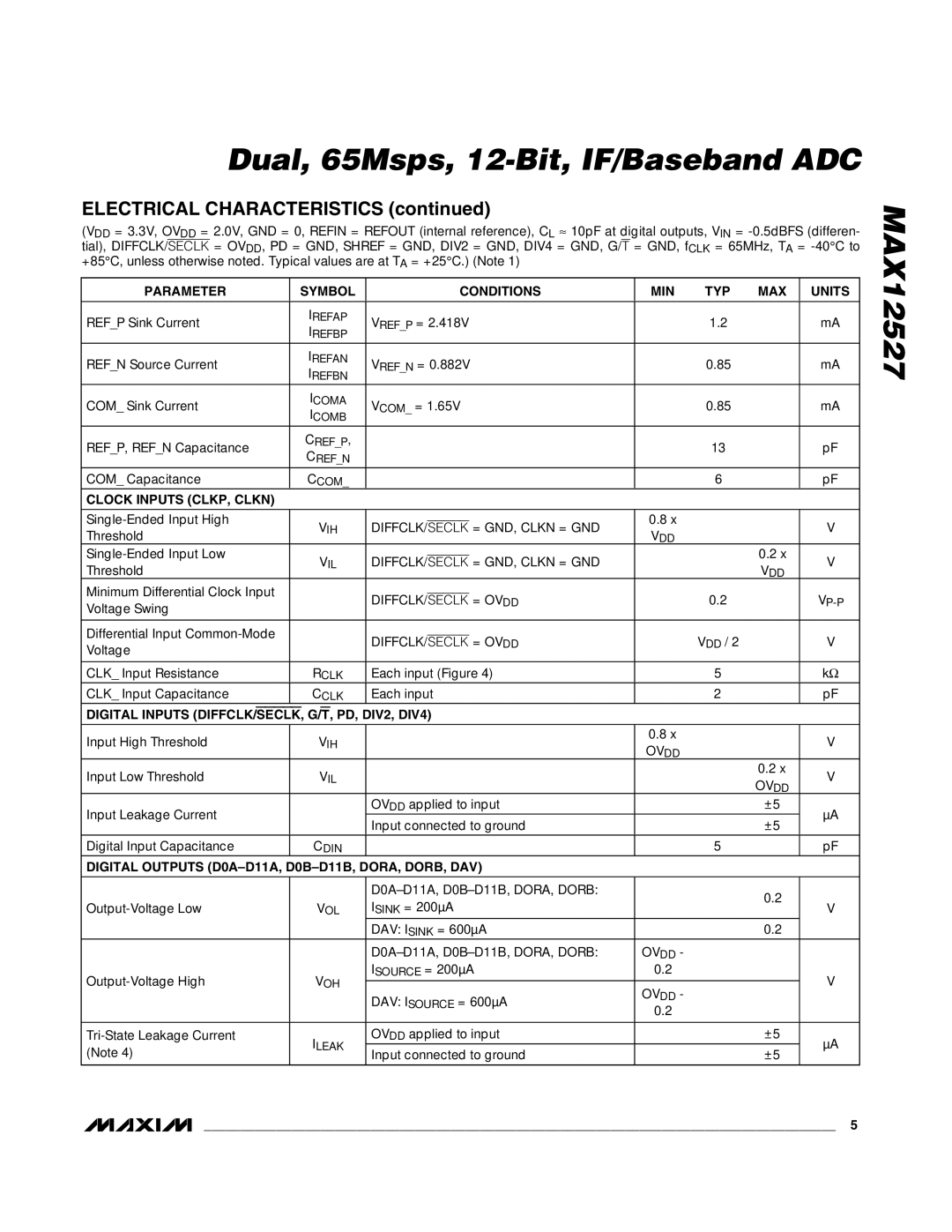

Dual, 65Msps, 12-Bit, IF/Baseband ADC

ELECTRICAL CHARACTERISTICS (continued)

(VDD = 3.3V, OVDD = 2.0V, GND = 0, REFIN = REFOUT (internal reference), CL ≈ 10pF at digital outputs, VIN =

+85°C, unless otherwise noted. Typical values are at TA = +25°C.) (Note 1)

PARAMETER |

| SYMBOL |

| CONDITIONS |

| MIN | TYP | MAX |

| UNITS |

|

|

|

| |||||||

|

|

|

|

|

|

|

|

|

|

|

REF_P Sink Current |

| IREFAP |

| VREF_P = 2.418V |

|

| 1.2 |

|

| mA |

| IREFBP |

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

REF_N Source Current |

| IREFAN |

| VREF_N = 0.882V |

|

| 0.85 |

|

| mA |

| IREFBN |

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

COM_ Sink Current |

| ICOMA |

| VCOM_ = 1.65V |

|

| 0.85 |

|

| mA |

| ICOMB |

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

REF_P, REF_N Capacitance |

| CREF_P, |

|

|

|

| 13 |

|

| pF |

| CREF_N |

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

COM_ Capacitance |

| CCOM_ |

|

|

|

| 6 |

|

| pF |

CLOCK INPUTS (CLKP, CLKN) |

|

|

|

|

|

|

|

|

|

|

| VIH |

| DIFFCLK/SECLK = GND, CLKN = GND |

| 0.8 x |

|

|

| V | |

Threshold |

|

|

| VDD |

|

|

| |||

|

|

|

|

|

|

|

|

| ||

| VIL |

| DIFFCLK/SECLK = GND, CLKN = GND |

|

|

| 0.2 x |

| V | |

Threshold |

|

|

|

|

| VDD |

| |||

|

|

|

|

|

|

|

|

| ||

Minimum Differential Clock Input |

|

|

| DIFFCLK/SECLK = OVDD |

|

| 0.2 |

|

| |

Voltage Swing |

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

Differential Input |

|

|

| DIFFCLK/SECLK = OVDD |

|

| VDD / 2 |

|

| V |

Voltage |

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

CLK_ Input Resistance |

| RCLK |

| Each input (Figure 4) |

|

| 5 |

|

| kΩ |

CLK_ Input Capacitance |

| CCLK |

| Each input |

|

| 2 |

|

| pF |

DIGITAL INPUTS (DIFFCLK/SECLK, G/T, PD, DIV2, DIV4) |

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

Input High Threshold |

| VIH |

|

|

| 0.8 x |

|

|

| V |

|

|

|

| OVDD |

|

|

| |||

|

|

|

|

|

|

|

|

|

| |

Input Low Threshold |

| VIL |

|

|

|

|

| 0.2 x |

| V |

|

|

|

|

|

| OVDD |

| |||

|

|

|

|

|

|

|

|

|

| |

Input Leakage Current |

|

|

| OVDD applied to input |

|

|

| ±5 |

| µA |

|

|

| Input connected to ground |

|

|

| ±5 |

| ||

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

Digital Input Capacitance |

| CDIN |

|

|

|

| 5 |

|

| pF |

DIGITAL OUTPUTS |

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 0.2 |

|

| |

| VOL |

| ISINK = 200µA |

|

|

|

| V | ||

|

|

|

|

|

|

| ||||

|

|

|

| DAV: ISINK = 600µA |

|

|

| 0.2 |

|

|

|

|

|

|

| OVDD - |

|

|

|

| |

| VOH |

| ISOURCE = 200µA |

| 0.2 |

|

|

| V | |

|

| DAV: ISOURCE = 600µA |

| OVDD - |

|

|

| |||

|

|

|

|

|

|

|

|

| ||

|

|

|

|

| 0.2 |

|

|

|

| |

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

| ILEAK |

| OVDD applied to input |

|

|

| ±5 |

| µA | |

(Note 4) |

|

| Input connected to ground |

|

|

| ±5 |

| ||

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

MAX12527

_______________________________________________________________________________________ 5