1

Board Level Hardware Description

The access timer logic is duplicated in the VMEchip2 and MCchip ASICs. Because the local bus timer in the VMEchip2 can detect an offboard access and the MCchip local bus timer cannot, the timer in the VMEchip2 is used in all cases except for the version of the MVME162 which does not include the VMEbus interface

Local Bus Arbiter

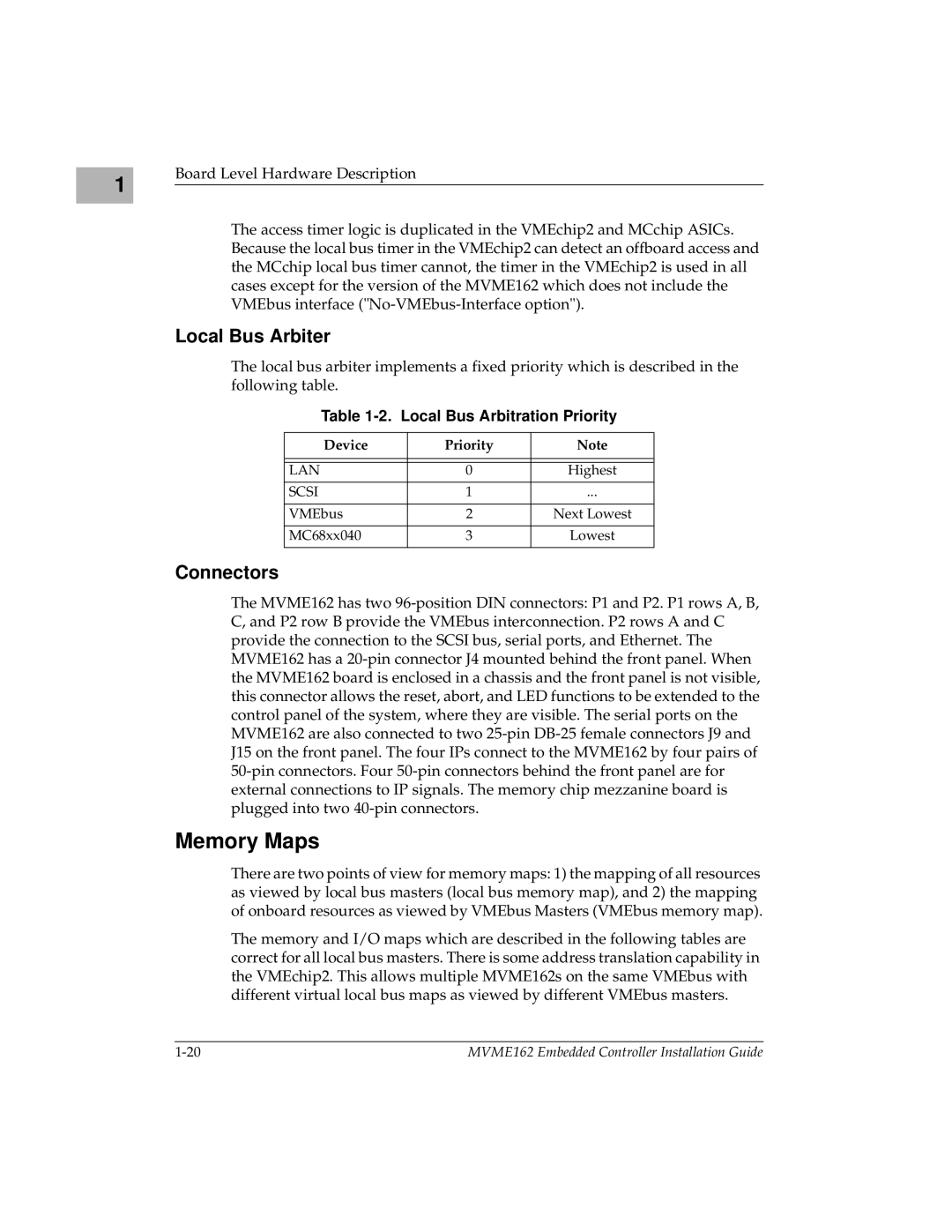

The local bus arbiter implements a fixed priority which is described in the following table.

Table 1-2. Local Bus Arbitration Priority

Device | Priority | Note | |

|

|

| |

|

|

|

|

LAN | 0 | Highest | |

|

|

|

|

SCSI | 1 | ... |

|

|

|

| |

VMEbus | 2 | Next Lowest | |

|

|

| |

MC68xx040 | 3 | Lowest | |

|

|

|

|

Connectors

The MVME162 has two

Memory Maps

There are two points of view for memory maps: 1) the mapping of all resources as viewed by local bus masters (local bus memory map), and 2) the mapping of onboard resources as viewed by VMEbus Masters (VMEbus memory map).

The memory and I/O maps which are described in the following tables are correct for all local bus masters. There is some address translation capability in the VMEchip2. This allows multiple MVME162s on the same VMEbus with different virtual local bus maps as viewed by different VMEbus masters.

MVME162 Embedded Controller Installation Guide |