Chapter 4 Functional Description

Device Controller Interface

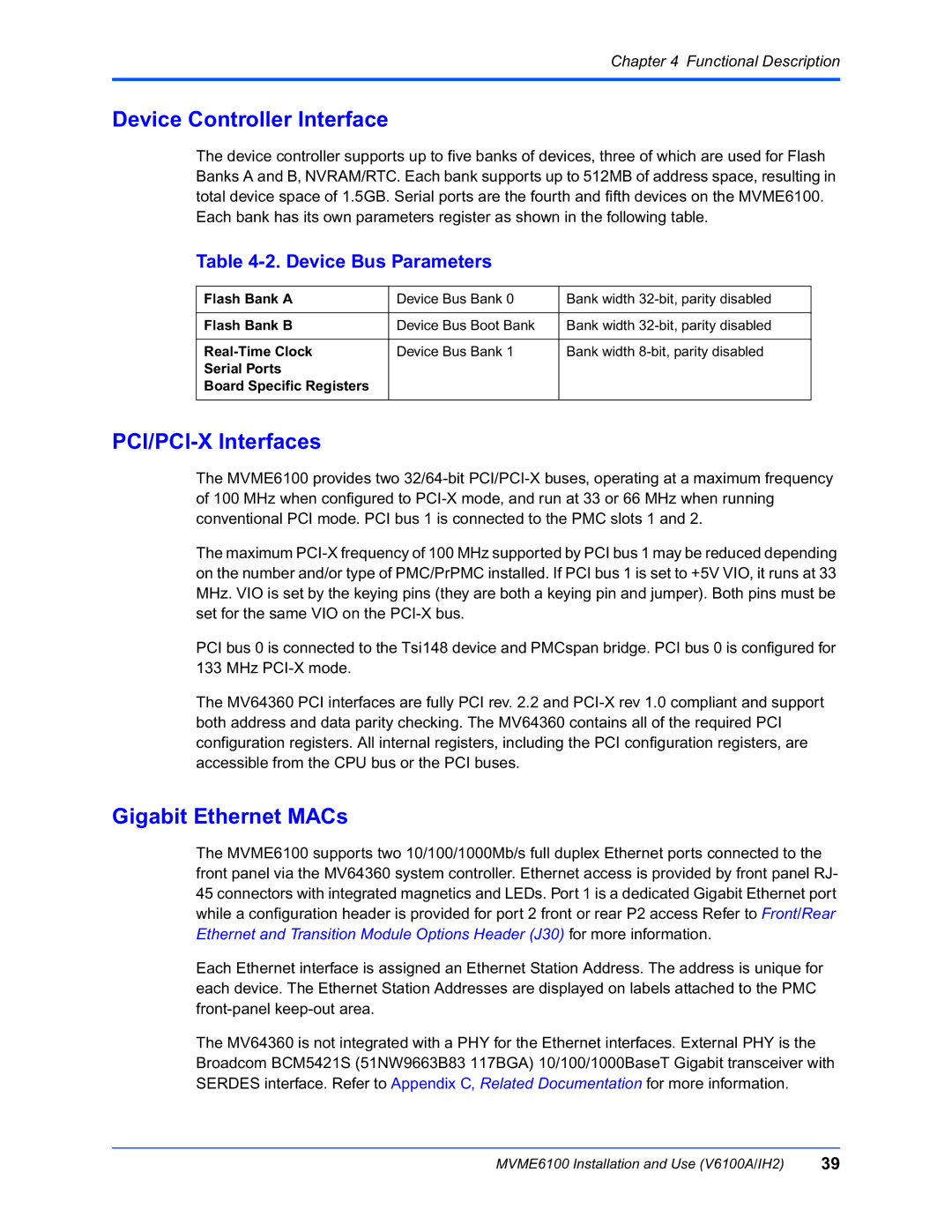

The device controller supports up to five banks of devices, three of which are used for Flash Banks A and B, NVRAM/RTC. Each bank supports up to 512MB of address space, resulting in total device space of 1.5GB. Serial ports are the fourth and fifth devices on the MVME6100. Each bank has its own parameters register as shown in the following table.

Table 4-2. Device Bus Parameters

Flash Bank A | Device Bus Bank 0 | Bank width |

|

|

|

Flash Bank B | Device Bus Boot Bank | Bank width |

|

|

|

Device Bus Bank 1 | Bank width | |

Serial Ports |

|

|

Board Specific Registers |

|

|

|

|

|

PCI/PCI-X Interfaces

The MVME6100 provides two

The maximum

PCI bus 0 is connected to the Tsi148 device and PMCspan bridge. PCI bus 0 is configured for 133 MHz

The MV64360 PCI interfaces are fully PCI rev. 2.2 and

Gigabit Ethernet MACs

The MVME6100 supports two 10/100/1000Mb/s full duplex Ethernet ports connected to the front panel via the MV64360 system controller. Ethernet access is provided by front panel RJ- 45 connectors with integrated magnetics and LEDs. Port 1 is a dedicated Gigabit Ethernet port while a configuration header is provided for port 2 front or rear P2 access Refer to Front/Rear Ethernet and Transition Module Options Header (J30) for more information.

Each Ethernet interface is assigned an Ethernet Station Address. The address is unique for each device. The Ethernet Station Addresses are displayed on labels attached to the PMC

The MV64360 is not integrated with a PHY for the Ethernet interfaces. External PHY is the Broadcom BCM5421S (51NW9663B83 117BGA) 10/100/1000BaseT Gigabit transceiver with SERDES interface. Refer to Appendix C, Related Documentation for more information.

MVME6100 Installation and Use (V6100A/IH2) | 39 |