Developer’s Guide

Embedded Modem MT5600SMI Family

SocketModem Developers Guide

Contents

114

Introduction

Product Description

Product Description Region

Developers Kit

Features

Sources of Additional Information

Technical Specifications

Maximum Component Height

Physical Dimensions

Available with or without LED Pins

Serial Pin Configurations

Pin Signal Description Name Type

Pin Descriptions for Serial SocketModem Devices

RXD

3V DC Power

Parallel Pin Configurations

Speaker, Call Monitor

Agnd GND

Electrical Characteristics

Handling Precautions

Absolute Maximum Ratings

Operating Conditions

Current and Power Requirements

Symbol Parameter Min Max Units

Parallel Host Bus Timing

Parallel Host Bus Timing Table

Parallel Host Bus Read Parallel Host Bus Write

Overview

SocketModem Parallel Interface

Register BIT No Name

Parallel Interface Registers

IER Interrupt Enable Register Addr = 1, Dlab =

Register Signal Definitions

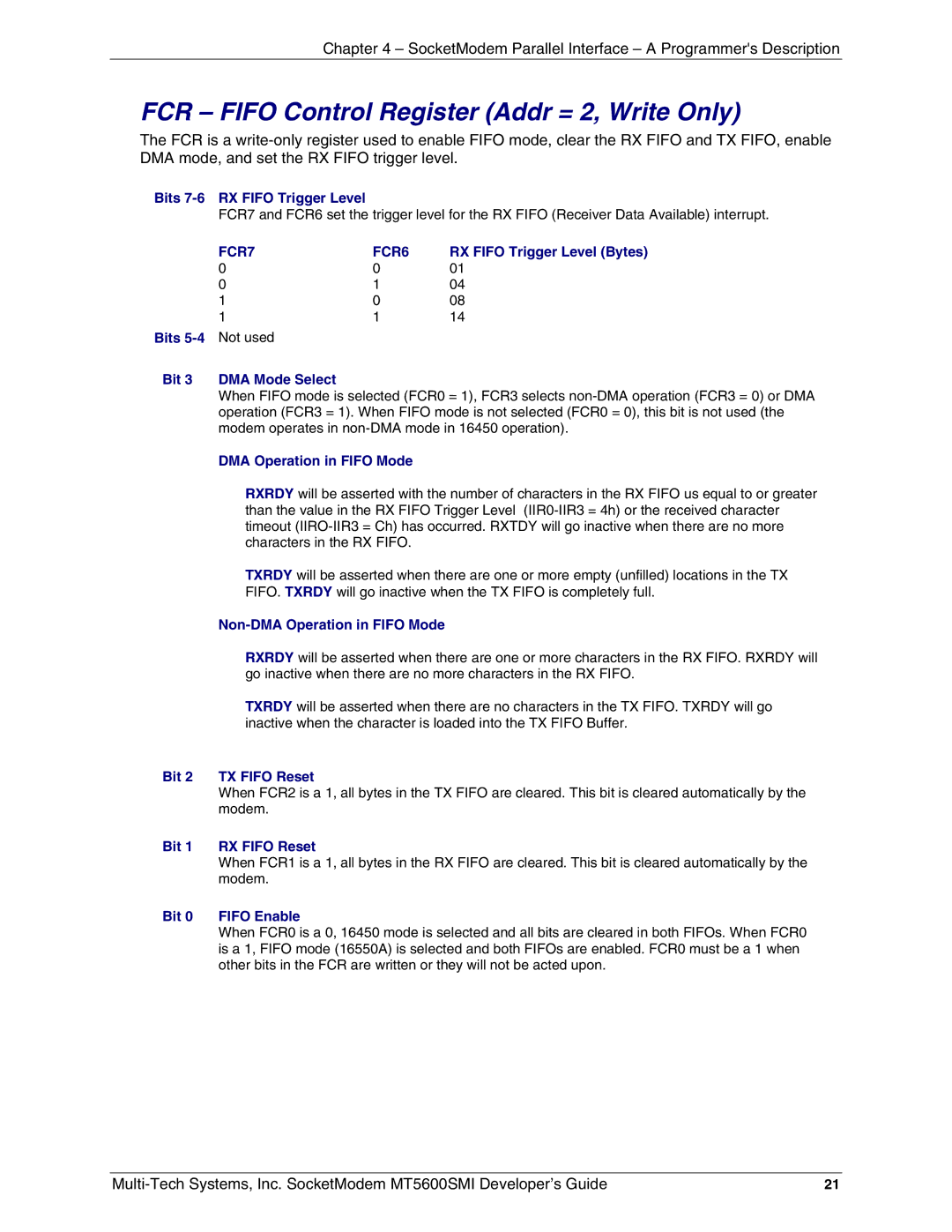

FCR7 FCR6

FCR Fifo Control Register Addr = 2, Write Only

Bit Interrupt Pending

IIR Interrupt Identifier Register Addr =

LCR Line Control Register Addr =

Bit 7 Divisor Latch Access Bit Dlab

Bit Data Terminal Ready DTR

MCR Modem Control Register Addr =

LSR Line Status Register Addr =

Bit 7 RX Fifo Error

RBX RX Buffer Receiver Buffer Register Addr = 0, Dlab =

MSR Modem Status Register Addr =

THR TX Buffer Transmitter Holding Register Addr = 0, Dlab =

Divisor Registers Addr = 0 and 1, Dlab =

Programmable Baud Rates

SCR Scratch Register Addr =

Receiver Fifo Interrupt Operation

Receiver Character Timeout Interrupts

Transmitter Fifo Interrupt Operation

Receiver Data Available Interrupt

AT Commands, S Registers, and Result Codes

Generic Modem Control Commands

Data Commands

Command Identification

Command Operating Mode Error Correction

Command

Request Manufacturer Identification

Command Restore Factory Configuration Profile

Country of Installation

Request Model Identification

Request Revision Identification

Command Designate a Default Reset Profile

Command Local Analog Loopback Test

Command Store Current Configuration

Command &Zn=x Store Telephone Number

Command Plug and Play Vendor ID and Product Number

Command Load Flash Memory

Procedure

Message Description

Upload Messages

Command E Command Echo

DTE-Modem Interface Commands

Command Q Quiet Result Code Control

Command Result Code Form

Command Extended Result Codes

Command Rlsd DCD Option

Command DTR Option

Command Flow Control

Command &S DSR Override

Command &R RTS/CTS Option

Command +IPR Fixed DTE Rate

+IPR?

Command +ILRR DTE-Modem Local Rate Reporting

Command +IFC DTE-Modem Local Flow Control

Call Control Commands

Command D Dial

Dial Modifiers

Command P Set Pulse Dial Default

Command T Set Tone Dial Default

Command Answer

Command Disconnect Hang-Up

Command Return to Online Data Mode

Command Speaker Control

Command Speaker Volume

Command Select Guard Tone

Command Select Pulse Dial Make/Break Ratio

Active Profile

AT&V

Stored Profile

Telephone Numbers

Command &V1 Display Last Connection Statistics

Termination Reason Local Request

Protocol Lapm Compression

Command Single Line Connect Message Enable

Command Report Line Signal Level

Command Report Line Signal Quality

Command -STE= Set Telephony Extension

Behavior in Data Mode +FCLASS=0

Behavior in Voice Mode +FCLASS=8

AT-STE=7

Examples

LINE-IN-USE

Connect

No Dial Tone

AT-STE=3

AT+FCLASS=8

AT+VTX Dlep

+MS Command Supported Rates

Command +MS Modulation Selection

Page

Modulation Reporting Control

+MR

Command Ccitt or Bell

Command Select µ-Law or A-Law Codec Type

Command +ES Error Control and Synchronous Mode Selection

Error Control Commands

Origrqst

Origfbk

Command +EB Break Handling in Error Control Operation

Command +ESR Selective Repeat

Command +EFCS Bit Frame Check Sequence

Error Control Reporting

Command +ER type Report the Current Error Control

Call Termination Buffer Management

Command Break Control

Command Transmit Break to Remote

Command -K MNP Extended Services

Data Compression Commands

Command +DS Data Compression

Command +DS44 Compression Select

Command +DR Data Compression Reporting

Command %C Enable/Disable Data Compression

Command +A8E V.8bis Operation Controls

V.8bis Commands

YYY

Command +A8I CI Signal Indication

Command #UD Last Call Status Report

Diagnostic Commands

Command Syntax

Data Call State Model

CallCleared codes from 3.6.4/V.58-1994

Monitoring an Active Connection

AT#UD Last Call Status Report Format Key Values Definition

Digits

Multimedia Modes Code Definition

Call Setup Result Codes Code Definition

DTE-DCE modes Code Definition

V.34 Info bit report Bits Source bits Definition

11. compressionActive from 3.2.2/V.58 Value Description

10. errorControl Active from 3.5.2/V.58 Value Description

Example Modem Response and Usage

Command Leased Line Operation

Compatibility Commands

Command Enable Cellular Power Level Adjustment

Command Initial Cellular Power Level Setting

92 +P and -Q Commands

FastConnect Commands

Command $F FastConnect Control

Command +PCW Call Waiting Enable

Initiate Modem-on-Hold

Modem-on-Hold Timer

Phase 1 and Phase 2 Control

PCM Upstream Ignore

Modem-on-Hold Hook Flash

Force Full Startup Procedure on Next Connection

Enable Quick Connect Profile Save

Use Short Sequence

Wait Time for Carrier, Silence, or Dial Tone

Registers

Carrier Detect Response Time Supported for backward

Test Mode Bit-Mapped Options Status Indicates the test

General Bit-Mapped Options Status Indicates the status

Reserved

Register Unit Range Default Description S21

Register Unit Range Default Description S27

Flow Control Bit-Mapped Options Status

Register Unit Range Default Description S36

General Bit-Mapped Options Status. Indicates the status

Register Unit Range Default Description S41

Pstn Transmit Attenuation Level. In non-PCM modes V.90 or

Register Unit Range Default Description S86

Register Unit Range Default Description S210

Short Form Long Form

Result Codes

+ER L APM

196 +MRR 197 198 199 200 201 202 203 204 205 206 207 208 209

DTE-to-Modem Transmit Data Stream

Fax I/O Processing

Modem-to-DTE Receive Data Stream

Characters Detected Action Taken

Fax Origination

Fax Mode Selection

Fax Answering

Fax Control Transmission

Fax Control Reception

Fax Data Reception

Fax Data Transmission

Commands and Parameters

Mode Entry Commands

Mode Commands

Mod Modulation Training Modulation Mode and Rate

Transmit Facsimile

Fax Class 1 and Fax Class 1.0 Modulation Modes and Rates

Command FTH Transmit Data with Hdlc Framing

Command +FRM Receive Facsimile

Command +FRH Receive Data with Hdlc Framing

Service Class 1 Commands

Command +FAR Adaptive Reception Control

Command +FCL Carrier Loss Timeout

DTE Inactivity Timeout

Double Escape Character Replacement

Command +FMI? Request Manufacturer Identification

Command +FPR Fixed DTE Rate

Command +FMM? Request Model Identification

Command +FMR? Request Revision Identification

Command +FLO Flow Control

Fax Class 1 Calling Sequence Transmitting a Single

Examples

Fax Class 1 Answering Sequence Receiving a Single

Voice Commands Overview

Voice Commands Function Configuration

Voice

DLE Shielded Event Codes Sent to the DTE

DLE Shielded Codes Sent to the Modem DCE

Can

102

Command +FCLASS=8 Select Voice Mode

Voice Configuration Commands

Command +VNH Automatic Hang-up Control

+VNH Command Behavior Command Response

Command +VIP Voice Initialize All Parameters

Basic Voice Commands

Command +VRX Start Modem Receive Record

Command +VTS Send Voice Tones

Command +VGR Voice Gain Receive Record Gain

Command +VTX Start Modem Transmit Playback

Example

105

Command +VGT Voice Gain Transmit Playback Volume

Command +VIT Voice Inactivity Timer DTE/Modem

106

+VLS Command Options

Command +VLS Analog Source/Destination Selection

Label Primitives Description

+VSP=1

108

S1T

Events Detectable in the Voice Mode per

Event Number Event Description Event Reporting

109

Command +VRN Ringback Never Appeared Timer

Command +VRA Ringback Goes Away Timer

Command +VSD Silence Detection Quiet and Silence

110

111

Command +VSM Compression Method Selection

Command +VTD Beep Tone Duration Timer

Command +VDR Distinctive Ring

112

113

Command +VDT Control Tone Cadence Reporting

114

Country Country Code

115

Test/Demo Board Components

Serial Test/Demo Board Block Diagram

Serial Test/Demo Board Block Diagram

5V / 3.3V Jumper JP6

116

Parallel Test/Demo Board Block Diagram

Parallel Test/Demo Board Block Diagram

117

Safety Certifications

Approvals Product Safety and EMC

Telecom Certifications

EMC Approvals

Regulatory Design Considerations

Hardware Considerations

119

120

EMC

Other Design Considerations

PC Board Layout Guidelines

121

Safety

Electromagnetic Interference EMI Considerations

122

123

5V Tolerant Inputs for 3.3V Modules

Regulatory Compliance

Regulatory Requirements for the United States

124

125

MT5600SMI

126

Current Label Content and Format as of August

127

Regulatory Requirements for Canada

128

IC XXXXXX-ZZZZZZZZ Where

New Zealand Telecom Warning Notice

South African Statement

129

EMC, Safety, and R&TTE Directive Compliance

International Modem Restrictions

130

131

Index

132

Enable quick connect profile save command -QCPS

133

Serial Test/Demo Board Components

134