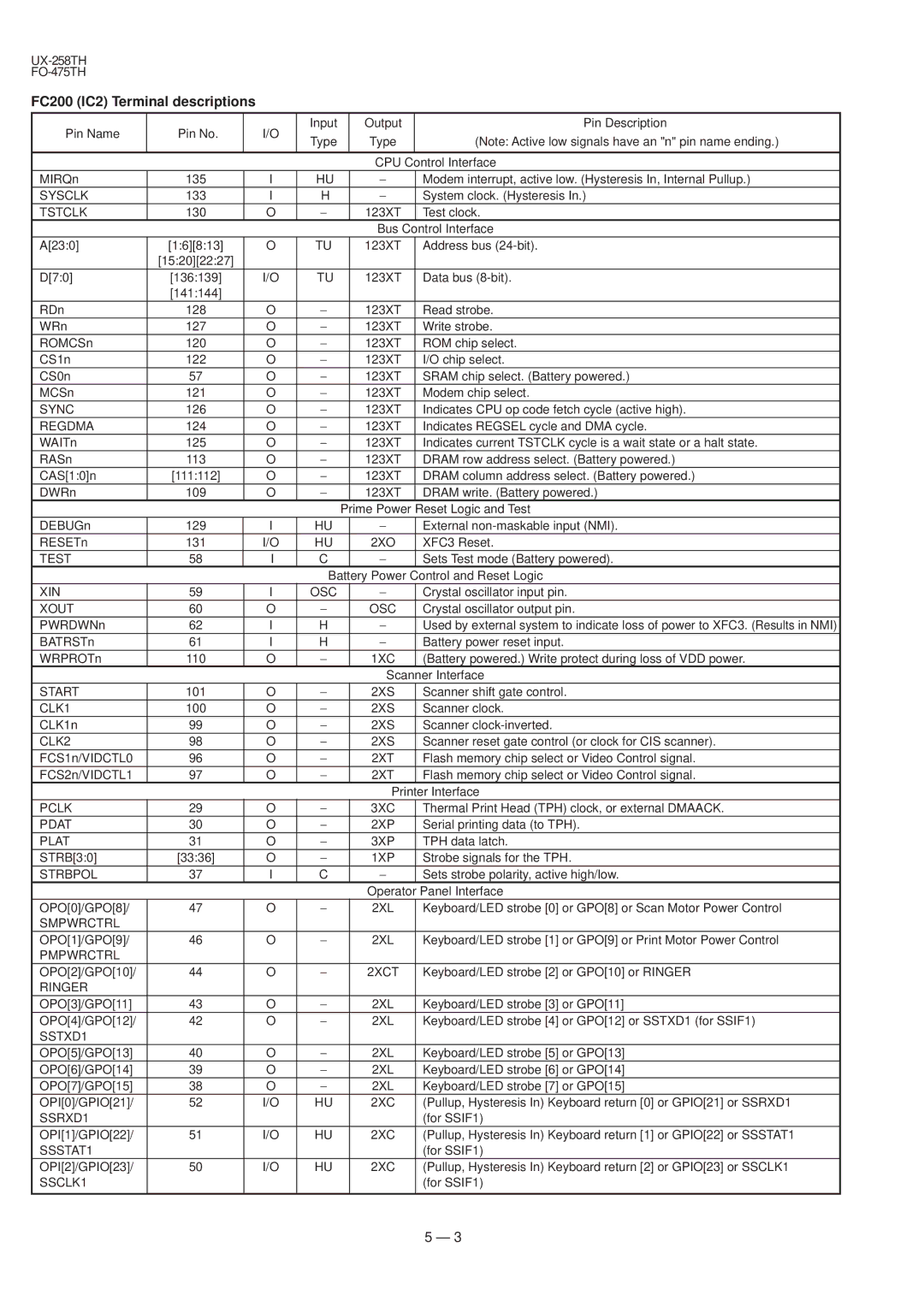

FC200 (IC2) Terminal descriptions

Pin Name | Pin No. | I/O | Input |

| Output | Pin Description |

Type |

| Type | (Note: Active low signals have an "n" pin name ending.) | |||

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

| CPU Control Interface | |

MIRQn | 135 | I | HU |

| − | Modem interrupt, active low. (Hysteresis In, Internal Pullup.) |

SYSCLK | 133 | I | H |

| − | System clock. (Hysteresis In.) |

TSTCLK | 130 | O | − |

| 123XT | Test clock. |

|

|

|

|

| Bus Control Interface | |

A[23:0] | [1:6][8:13] | O | TU |

| 123XT | Address bus |

| [15:20][22:27] |

|

|

|

|

|

D[7:0] | [136:139] | I/O | TU |

| 123XT | Data bus |

| [141:144] |

|

|

|

|

|

RDn | 128 | O | − |

| 123XT | Read strobe. |

WRn | 127 | O | − |

| 123XT | Write strobe. |

ROMCSn | 120 | O | − |

| 123XT | ROM chip select. |

CS1n | 122 | O | − |

| 123XT | I/O chip select. |

CS0n | 57 | O | − |

| 123XT | SRAM chip select. (Battery powered.) |

MCSn | 121 | O | − |

| 123XT | Modem chip select. |

SYNC | 126 | O | − |

| 123XT | Indicates CPU op code fetch cycle (active high). |

REGDMA | 124 | O | − |

| 123XT | Indicates REGSEL cycle and DMA cycle. |

WAITn | 125 | O | − |

| 123XT | Indicates current TSTCLK cycle is a wait state or a halt state. |

RASn | 113 | O | − |

| 123XT | DRAM row address select. (Battery powered.) |

CAS[1:0]n | [111:112] | O | − |

| 123XT | DRAM column address select. (Battery powered.) |

DWRn | 109 | O | − |

| 123XT | DRAM write. (Battery powered.) |

|

|

|

| Prime Power Reset Logic and Test | ||

DEBUGn | 129 | I | HU |

| − | External |

RESETn | 131 | I/O | HU |

| 2XO | XFC3 Reset. |

TEST | 58 | I | C |

| − | Sets Test mode (Battery powered). |

|

|

| Battery Power Control and Reset Logic | |||

XIN | 59 | I | OSC |

| − | Crystal oscillator input pin. |

XOUT | 60 | O | − |

| OSC | Crystal oscillator output pin. |

PWRDWNn | 62 | I | H |

| − | Used by external system to indicate loss of power to XFC3. (Results in NMI) |

BATRSTn | 61 | I | H |

| − | Battery power reset input. |

WRPROTn | 110 | O | − |

| 1XC | (Battery powered.) Write protect during loss of VDD power. |

|

|

|

|

| Scanner Interface | |

START | 101 | O | − |

| 2XS | Scanner shift gate control. |

CLK1 | 100 | O | − |

| 2XS | Scanner clock. |

CLK1n | 99 | O | − |

| 2XS | Scanner |

CLK2 | 98 | O | − |

| 2XS | Scanner reset gate control (or clock for CIS scanner). |

FCS1n/VIDCTL0 | 96 | O | − |

| 2XT | Flash memory chip select or Video Control signal. |

FCS2n/VIDCTL1 | 97 | O | − |

| 2XT | Flash memory chip select or Video Control signal. |

|

|

|

|

| Printer Interface | |

PCLK | 29 | O | − |

| 3XC | Thermal Print Head (TPH) clock, or external DMAACK. |

PDAT | 30 | O | − |

| 2XP | Serial printing data (to TPH). |

PLAT | 31 | O | − |

| 3XP | TPH data latch. |

STRB[3:0] | [33:36] | O | − |

| 1XP | Strobe signals for the TPH. |

STRBPOL | 37 | I | C |

| − | Sets strobe polarity, active high/low. |

|

|

|

|

| Operator Panel Interface | |

OPO[0]/GPO[8]/ | 47 | O | − |

| 2XL | Keyboard/LED strobe [0] or GPO[8] or Scan Motor Power Control |

SMPWRCTRL |

|

|

|

|

|

|

OPO[1]/GPO[9]/ | 46 | O | − |

| 2XL | Keyboard/LED strobe [1] or GPO[9] or Print Motor Power Control |

PMPWRCTRL |

|

|

|

|

|

|

OPO[2]/GPO[10]/ | 44 | O | − |

| 2XCT | Keyboard/LED strobe [2] or GPO[10] or RINGER |

RINGER |

|

|

|

|

|

|

OPO[3]/GPO[11] | 43 | O | − |

| 2XL | Keyboard/LED strobe [3] or GPO[11] |

OPO[4]/GPO[12]/ | 42 | O | − |

| 2XL | Keyboard/LED strobe [4] or GPO[12] or SSTXD1 (for SSIF1) |

SSTXD1 |

|

|

|

|

|

|

OPO[5]/GPO[13] | 40 | O | − |

| 2XL | Keyboard/LED strobe [5] or GPO[13] |

OPO[6]/GPO[14] | 39 | O | − |

| 2XL | Keyboard/LED strobe [6] or GPO[14] |

OPO[7]/GPO[15] | 38 | O | − |

| 2XL | Keyboard/LED strobe [7] or GPO[15] |

OPI[0]/GPIO[21]/ | 52 | I/O | HU |

| 2XC | (Pullup, Hysteresis In) Keyboard return [0] or GPIO[21] or SSRXD1 |

SSRXD1 |

|

|

|

|

| (for SSIF1) |

OPI[1]/GPIO[22]/ | 51 | I/O | HU |

| 2XC | (Pullup, Hysteresis In) Keyboard return [1] or GPIO[22] or SSSTAT1 |

SSSTAT1 |

|

|

|

|

| (for SSIF1) |

OPI[2]/GPIO[23]/ | 50 | I/O | HU |

| 2XC | (Pullup, Hysteresis In) Keyboard return [2] or GPIO[23] or SSCLK1 |

SSCLK1 |

|

|

|

|

| (for SSIF1) |

|

|

|

|

|

|

|

5 – 3