SUPER X5DL8-GG/X5DLR-8G2+/X5DLR-8G2 User’s Manual

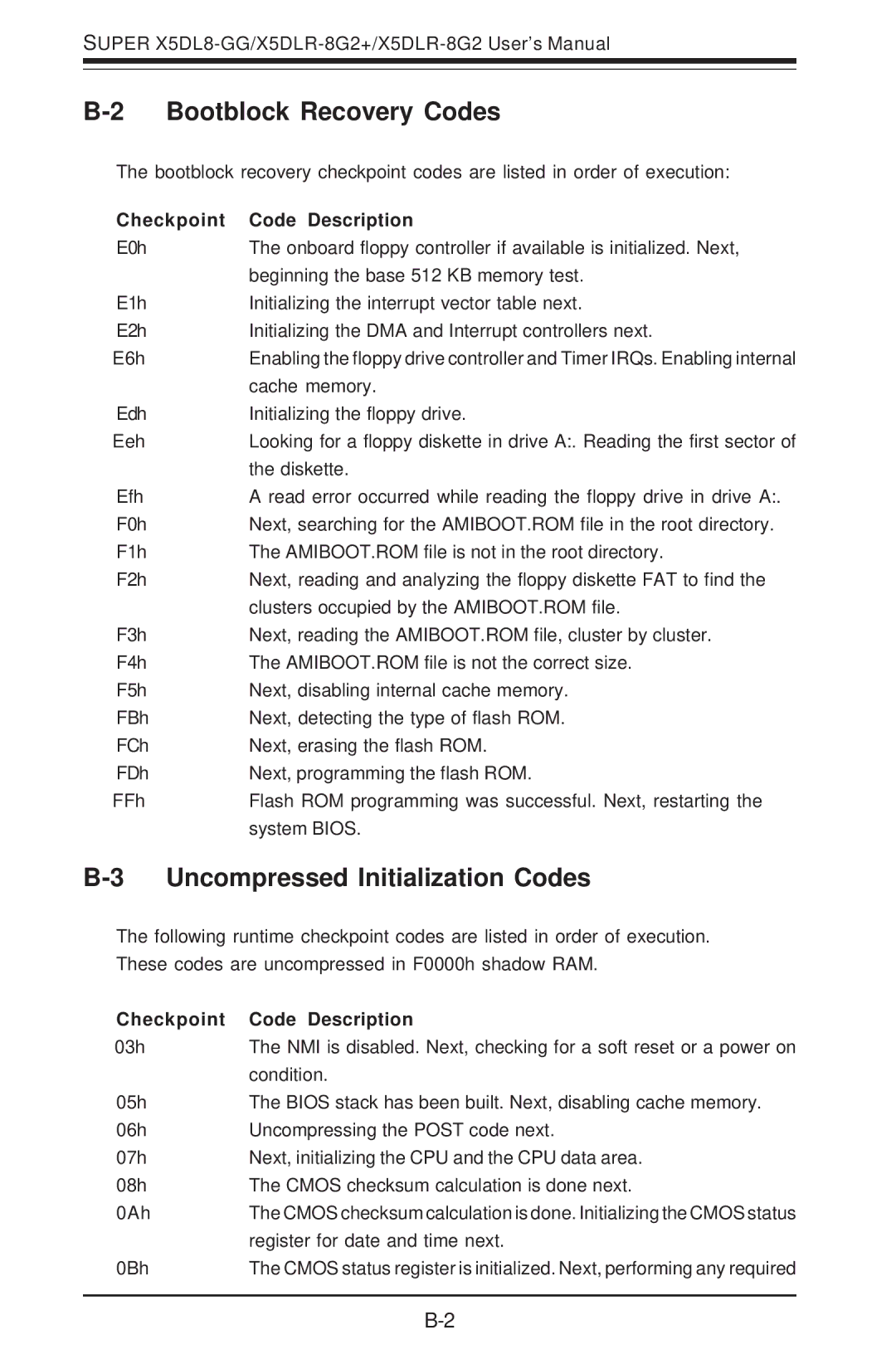

B-2 Bootblock Recovery Codes

The bootblock recovery checkpoint codes are listed in order of execution:

Checkpoint | Code Description |

E0h | The onboard floppy controller if available is initialized. Next, |

| beginning the base 512 KB memory test. |

E1h | Initializing the interrupt vector table next. |

E2h | Initializing the DMA and Interrupt controllers next. |

E6h | Enabling the floppy drive controller and Timer IRQs. Enabling internal |

| cache memory. |

Edh | Initializing the floppy drive. |

Eeh | Looking for a floppy diskette in drive A:. Reading the first sector of |

| the diskette. |

Efh | A read error occurred while reading the floppy drive in drive A:. |

F0h | Next, searching for the AMIBOOT.ROM file in the root directory. |

F1h | The AMIBOOT.ROM file is not in the root directory. |

F2h | Next, reading and analyzing the floppy diskette FAT to find the |

| clusters occupied by the AMIBOOT.ROM file. |

F3h | Next, reading the AMIBOOT.ROM file, cluster by cluster. |

F4h | The AMIBOOT.ROM file is not the correct size. |

F5h | Next, disabling internal cache memory. |

FBh | Next, detecting the type of flash ROM. |

FCh | Next, erasing the flash ROM. |

FDh | Next, programming the flash ROM. |

FFh | Flash ROM programming was successful. Next, restarting the |

| system BIOS. |

B-3 Uncompressed Initialization Codes

The following runtime checkpoint codes are listed in order of execution. These codes are uncompressed in F0000h shadow RAM.

Checkpoint | Code Description |

03h | The NMI is disabled. Next, checking for a soft reset or a power on |

| condition. |

05h | The BIOS stack has been built. Next, disabling cache memory. |

06h | Uncompressing the POST code next. |

07h | Next, initializing the CPU and the CPU data area. |

08h | The CMOS checksum calculation is done next. |

0Ah | The CMOS checksum calculation is done. Initializing the CMOS status |

| register for date and time next. |

0Bh | The CMOS status register is initialized. Next, performing any required |