Chapter 4: AMIBIOS

4-5 Chipset Setup

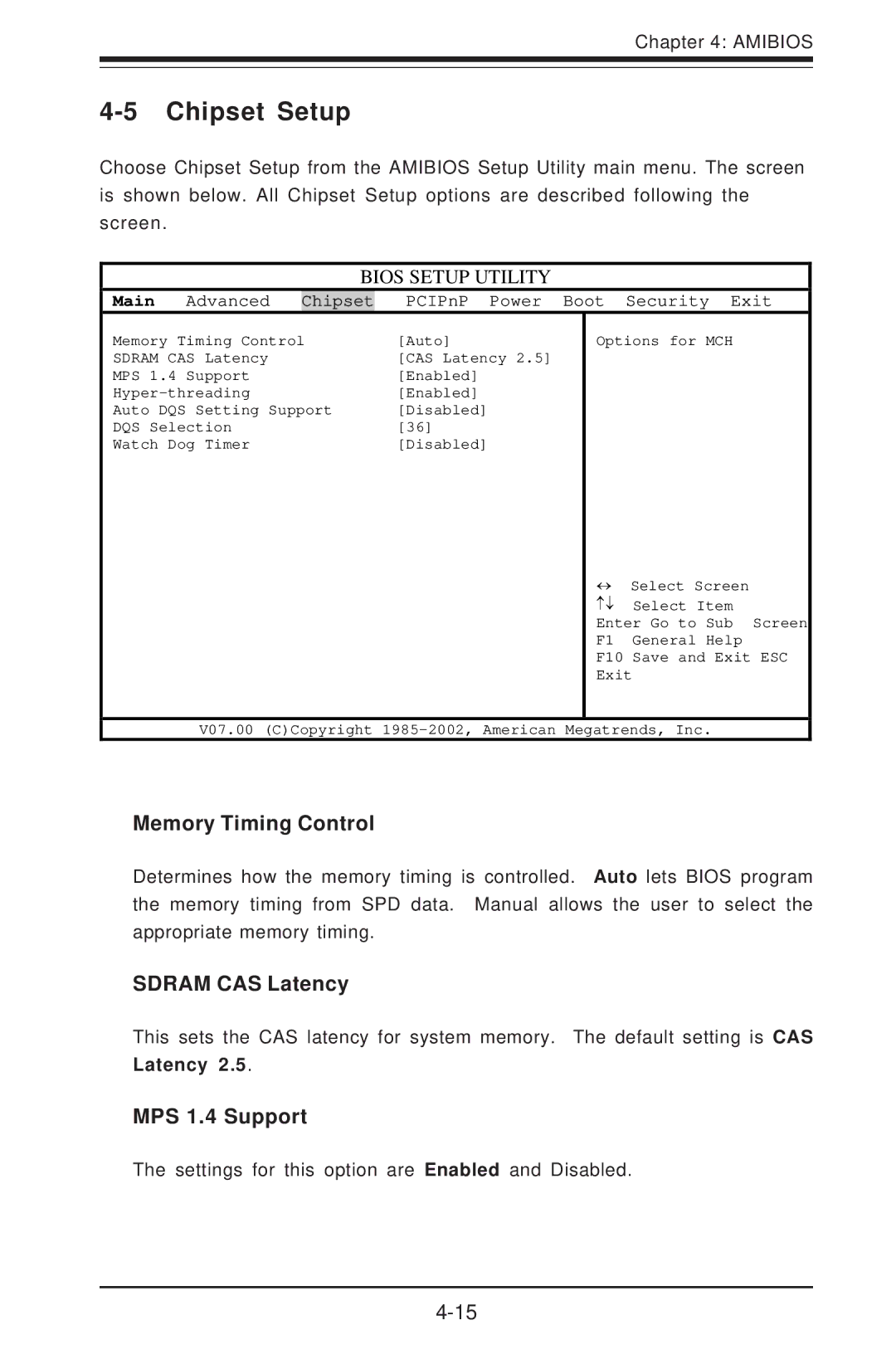

Choose Chipset Setup from the AMIBIOS Setup Utility main menu. The screen is shown below. All Chipset Setup options are described following the screen.

BIOS SETUP UTILITY

Main Advanced Chipset PCIPnP Power Boot Security Exit

Memory Timing Control | [Auto] |

SDRAM CAS Latency | [CAS Latency 2.5] |

MPS 1.4 Support | [Enabled] |

[Enabled] | |

Auto DQS Setting Support | [Disabled] |

DQS Selection | [36] |

Watch Dog Timer | [Disabled] |

Options for MCH

↔Select Screen ↑↓ Select Item

Enter Go to Sub Screen F1 General Help

F10 Save and Exit ESC Exit

V07.00 (C)Copyright

Memory Timing Control

Determines how the memory timing is controlled. Auto lets BIOS program the memory timing from SPD data. Manual allows the user to select the appropriate memory timing.

SDRAM CAS Latency

This sets the CAS latency for system memory. The default setting is CAS

Latency 2.5.

MPS 1.4 Support

The settings for this option are Enabled and Disabled.