MSP430x11x1

MIXED SIGNAL MICROCONTROLLER

SLAS241C ± SEPTEMBER 1999 ± REVISED JUNE 2000

flash memory

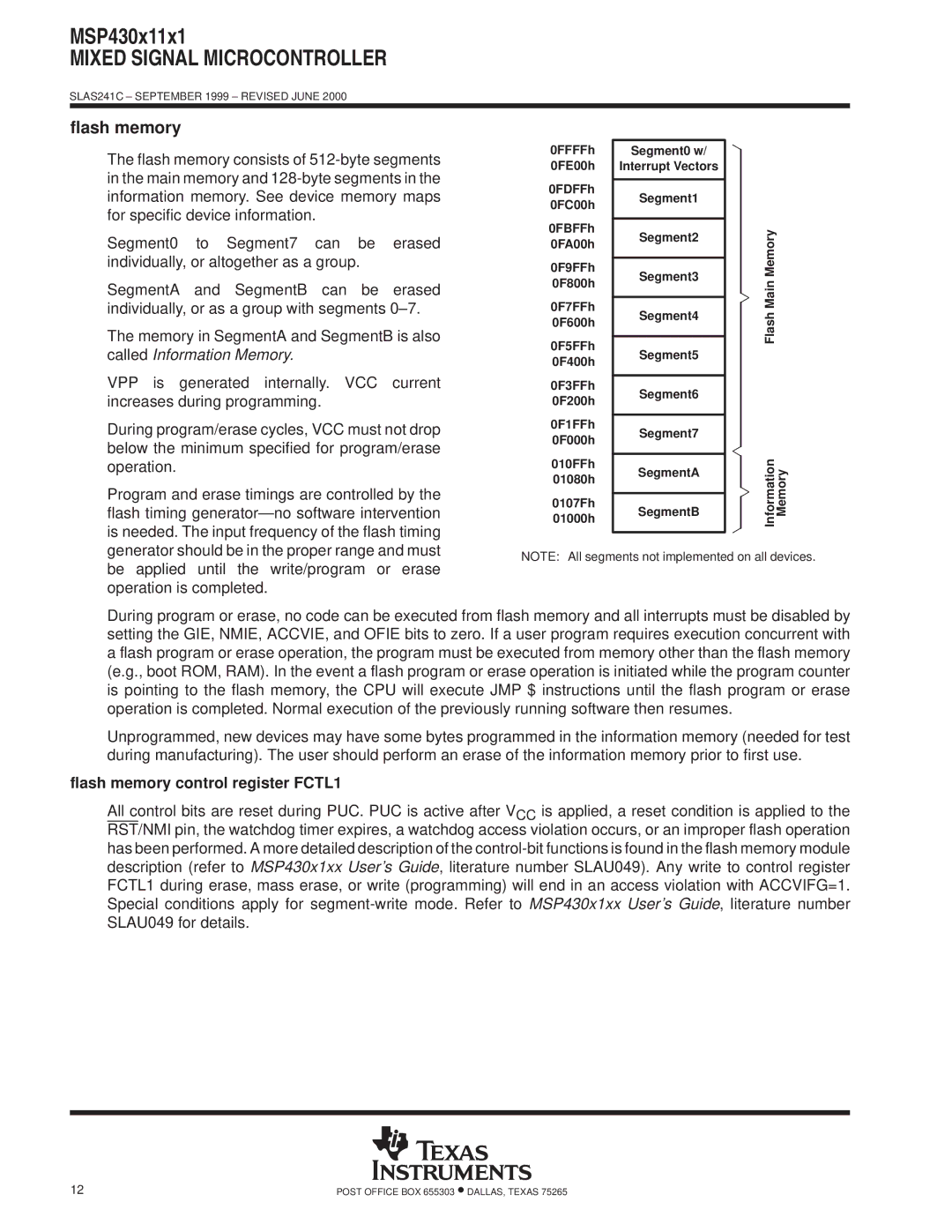

The flash memory consists of

Segment0 to Segment7 can be erased individually, or altogether as a group.

SegmentA and SegmentB can be erased individually, or as a group with segments 0±7.

The memory in SegmentA and SegmentB is also called Information Memory.

VPP is generated internally. VCC current increases during programming.

During program/erase cycles, VCC must not drop below the minimum specified for program/erase operation.

Program and erase timings are controlled by the flash timing generatorÐno software intervention is needed. The input frequency of the flash timing generator should be in the proper range and must be applied until the write/program or erase operation is completed.

0FFFFh | Segment0 w/ |

|

| |

|

| |||

0FE00h | Interrupt Vectors |

|

| |

0FDFFh |

|

|

| |

Segment1 |

|

| ||

0FC00h |

|

| ||

|

|

| ||

0FBFFh |

|

| Memory | |

Segment2 |

| |||

0FA00h |

| |||

|

| |||

|

|

| ||

0F9FFh |

|

|

| |

Segment3 |

|

| ||

0F800h |

| Main | ||

|

| |||

0F7FFh |

|

| ||

Segment4 | ||||

| ||||

| Flash | |||

0F600h |

| |||

|

| |||

|

|

| ||

0F5FFh |

|

|

| |

Segment5 |

|

| ||

0F400h |

|

| ||

|

|

| ||

0F3FFh |

|

|

| |

Segment6 |

|

| ||

0F200h |

|

| ||

|

|

| ||

0F1FFh |

|

|

| |

Segment7 |

|

| ||

0F000h |

|

| ||

|

|

| ||

010FFh |

|

| Information Memory | |

SegmentA |

| |||

|

| |||

01080h |

|

| ||

|

|

| ||

0107Fh |

|

|

| |

SegmentB |

|

| ||

|

| |||

01000h |

|

| ||

|

|

| ||

|

|

|

|

NOTE: All segments not implemented on all devices.

During program or erase, no code can be executed from flash memory and all interrupts must be disabled by setting the GIE, NMIE, ACCVIE, and OFIE bits to zero. If a user program requires execution concurrent with a flash program or erase operation, the program must be executed from memory other than the flash memory (e.g., boot ROM, RAM). In the event a flash program or erase operation is initiated while the program counter is pointing to the flash memory, the CPU will execute JMP $ instructions until the flash program or erase operation is completed. Normal execution of the previously running software then resumes.

Unprogrammed, new devices may have some bytes programmed in the information memory (needed for test during manufacturing). The user should perform an erase of the information memory prior to first use.

flash memory control register FCTL1

All control bits are reset during PUC. PUC is active after VCC is applied, a reset condition is applied to the

RST/NMI pin, the watchdog timer expires, a watchdog access violation occurs, or an improper flash operation has been performed. A more detailed description of the

12 | POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |