Tssop

MSP430x11x1

Description

Functional block diagram

Available Options Packaged Devices

PIN Sowb PIN Tssop

Pulldown resistor of 30 k Ω is needed on F11x1

Terminal Functions

Short-form description

Processing unit

Terminal Description Name

Address Mode Descriptions

CPU

Instruction set

Instruction Word Formats

Low-power consumption capabilities

Operation modes and interrupts

Status register R2

SCG1

SCG0

SCG1 SCG0

Interrupt vector addresses

Caifg

Wdtifg

CCIFG1, CCIFG2, Taifg

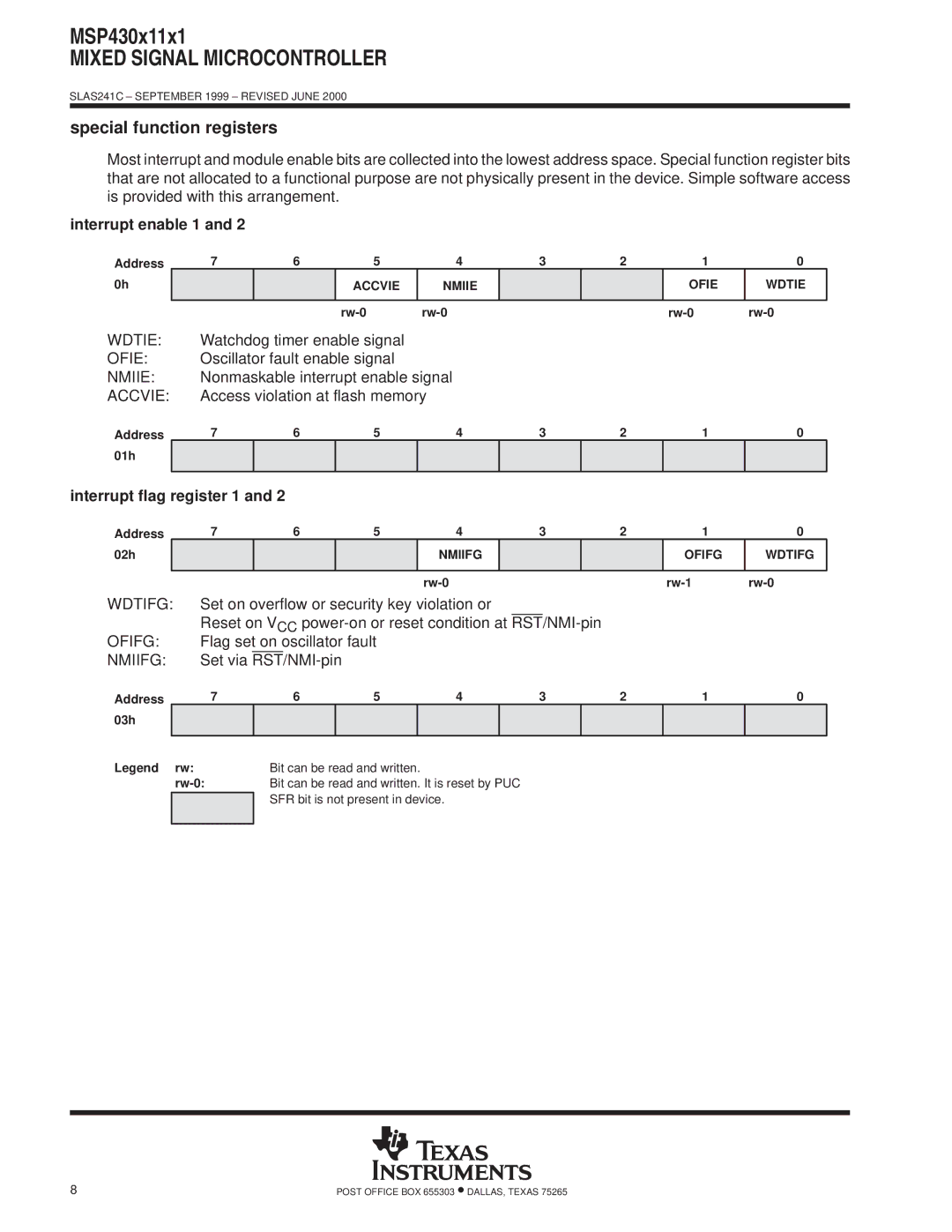

Special function registers

Wdtifg

Ofifg

Nmiifg

Memory organization

Boot ROM containing bootstrap loader

Functions of the bootstrap loader

Features of the bootstrap loader are

Hardware resources used for serial input/output

WDT

VCC RST/NMI PIN Test PIN

Bootstrap loader Starts

VCC

Test

Internal

Flash memory

Flash memory control register FCTL1

WRT

Flash memory, timing generator, control register FCTL2

Erase 0128h, bit1, Erase a segment

Flash memory control register FCTL3

FN0±FN5

SSEL0, SSEL1

Aclk

Busy

Keyv

Accvifg

Wait

Emex

Flash memory, interrupt and security key violation

Lock

Accv

PUC

POR

Nmirs

Peripherals

Oscillator and system clock

Clock Signals

Digital I/O

Watchdog timer

TimerA Three capture/compare registers

TimerA 3 capture/compare registers

TimerA, MSP430x11x1 Configuration

ComparatorA

Caout

CAF

CACTL2.4

CATCTL2.7

Slope a/d conversion

CACTL1

Caex Caon Caies Caifg Rsel REF1 REF0

CACTL2

Peripheral file map

Peripherals with Word Access

Peripherals with Byte Access

MIN NOM MAX Units

Absolute maximum ratings²

Recommended operating conditions

MSP430x11x1 Devices

Frequency vs Supply Voltage

Parameter Test Conditions MIN TYP MAX Unit

IAM

ILPM2

ILPM3

Outputs Port 1 to P2 P1.0 to P1.7, P2.0 to P2.5

Leakage current

Internal signals TAx, Smclk at TimerA

Inputs Px.x, TAx

Parameter Test Conditions VCC MIN TYP MAX Unit

Port P1, P2 P1.x to P2.x

Outputs P1.x, P2.x, TAx

ComparatorA see Note

VRefVT vs Temperature, VCC = 3 V, C1121

VRefVT vs Temperature, VCC = 2.2 V, C1121

PUC/POR

CAF Caon

RAM

Parameter MIN NOM MAX Unit

DCO

Variance Max

Dcoclk

DCO Steps

JTAG/programming

Principle characteristics of the DCO

Wake-up from lower power modes LPMx

GND

Input/output schematic

Port P1, P1.0 to P1.3, input/output with Schmitt-trigger

P1DIR.4 P1OUT.4 Smclk

P1IFG.4 P1IES.4

P1DIR.5 P1OUT.5

P1IFG.5 P1IES.5

Port P2, P2.0 to P2.2, input/output with Schmitt-trigger

CAPD.X

Port P2, P2.3 to P2.4, input/output with Schmitt-trigger

P2DIR.3 P2OUT.3

P2IFG.3 P1IES.3

P2DIR.4 P2OUT.4

P2SEL.5 VCC

P2DIR.5

P2OUT.5

P2IRQ.5

Port P2, unbonded bits P2.6 and P2.7

Pins DIM MAX

DW R-PDSO-G

Plastic SMALL-OUTLINE Package

PIN Shown

Pins Shown

Pins DIM MAX MIN

PW R-PDSO-G Plastic SMALL-OUTLINE Package

15 NOM Gage Plane Seating Plane 20 MAX

Important Notice