MSP430x11x1

MIXED SIGNAL MICROCONTROLLER

SLAS241C ± SEPTEMBER 1999 ± REVISED JUNE 2000

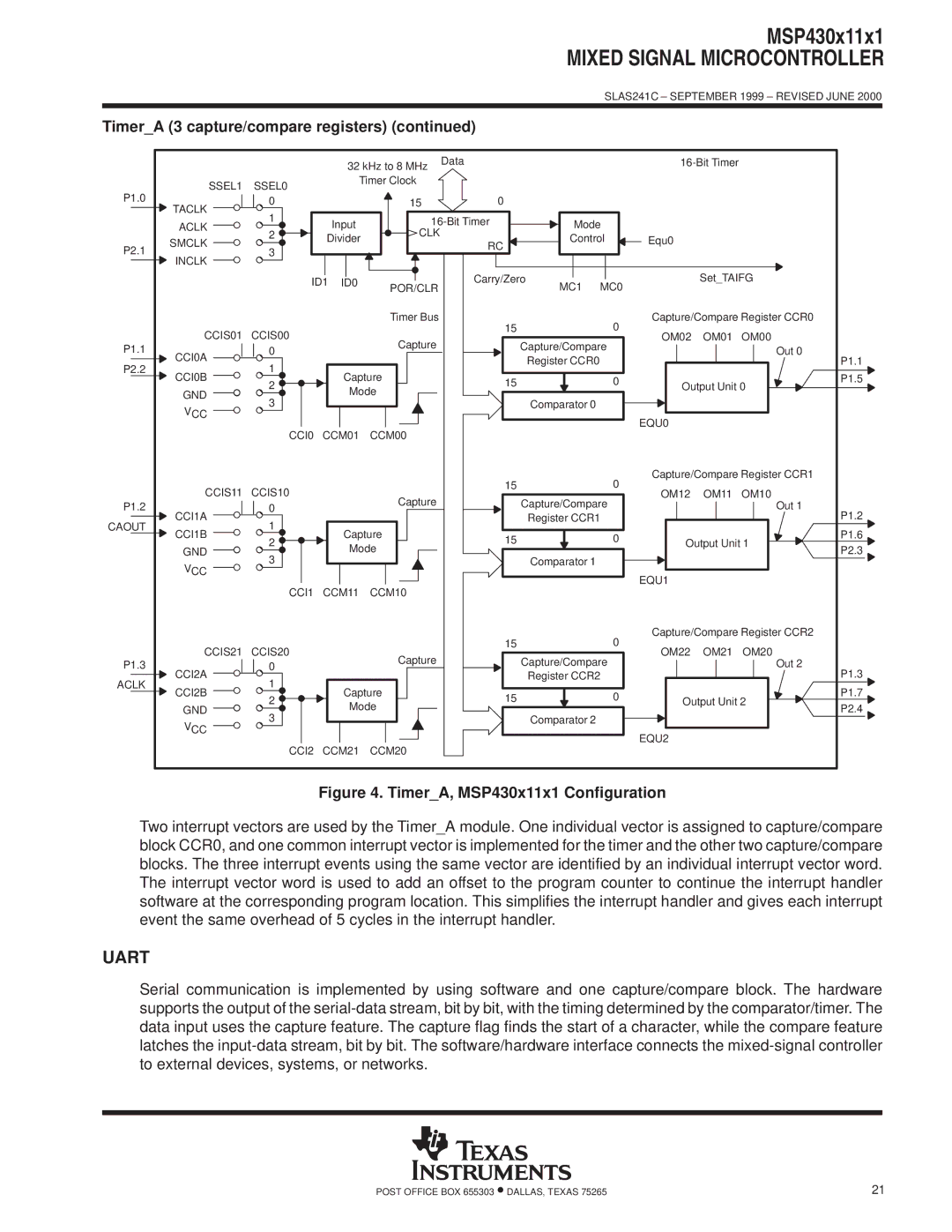

Timer_A (3 capture/compare registers) (continued)

|

| 32 kHz to 8 MHz | Data |

| |||

|

|

|

|

| |||

SSEL1 | SSEL0 |

| Timer Clock |

|

|

| |

|

|

|

|

|

| ||

P1.0 | 0 |

|

| 15 | 0 |

|

|

TACLK | 1 |

|

|

|

|

|

|

ACLK | Input |

|

| Mode |

| ||

2 |

|

|

| ||||

SMCLK | Divider | CLK | Control | Equ0 | |||

|

| RC | |||||

3 |

|

|

|

| |||

P2.1 |

|

|

|

|

|

| |

INCLK |

|

|

|

|

|

|

|

ID1 | ID0 | Carry/Zero | Set_TAIFG | |

POR/CLR | MC1 MC0 | |||

|

|

|

|

| Timer Bus | 15 | 0 | Capture/Compare Register CCR0 | ||

CCIS01 | CCIS00 |

|

| OM02 | OM01 | OM00 | ||

| Capture |

| Capture/Compare | |||||

P1.1 | 0 |

|

|

|

| Out 0 | ||

|

|

|

|

| ||||

CCI0A | 1 |

|

|

| Register CCR0 |

|

| P1.1 |

P2.2 |

|

|

|

|

| |||

Capture |

|

|

|

| P1.5 | |||

CCI0B | 2 | 15 | 0 |

|

| |||

GND | Mode | Output Unit 0 | ||||||

3 |

|

|

|

|

| |||

|

|

| Comparator 0 |

|

|

| ||

VCC |

|

|

|

|

|

| ||

|

|

|

|

| EQU0 |

|

| |

|

|

|

|

|

|

|

| |

| CCI0 | CCM01 | CCM00 |

|

|

|

|

|

|

|

|

| 15 | 0 | Capture/Compare Register CCR1 | ||

CCIS11 | CCIS10 |

|

| OM12 | OM11 | OM10 | ||

| Capture |

| Capture/Compare | |||||

P1.2 | 0 |

|

|

|

| Out 1 | ||

|

|

|

|

| ||||

CCI1A | 1 |

|

|

| Register CCR1 |

|

| P1.2 |

CAOUT | Capture |

|

|

|

| P1.6 | ||

CCI1B | 2 | 15 | 0 |

|

| |||

GND | Mode | Output Unit 1 | ||||||

3 |

| Comparator 1 |

|

| P2.3 | |||

VCC |

|

|

|

|

|

| ||

|

|

|

|

| EQU1 |

|

| |

|

|

|

|

|

|

|

| |

| CCI1 | CCM11 | CCM10 |

|

|

|

|

|

|

|

|

| 15 | 0 | Capture/Compare Register CCR2 | ||

CCIS21 | CCIS20 |

|

| OM22 | OM21 | OM20 | ||

| Capture |

| Capture/Compare | |||||

P1.3 | 0 |

|

|

|

| Out 2 | ||

|

|

|

|

| ||||

CCI2A | 1 |

|

|

| Register CCR2 |

|

| P1.3 |

ACLK | Capture |

|

|

|

| P1.7 | ||

CCI2B | 2 | 15 | 0 |

|

| |||

GND | Mode | Output Unit 2 | ||||||

3 |

| Comparator 2 |

|

| P2.4 | |||

VCC |

|

|

|

|

|

| ||

|

|

|

|

| EQU2 |

|

| |

|

|

|

|

|

|

|

| |

| CCI2 | CCM21 | CCM20 |

|

|

|

|

|

Figure 4. Timer_A, MSP430x11x1 Configuration

Two interrupt vectors are used by the Timer_A module. One individual vector is assigned to capture/compare block CCR0, and one common interrupt vector is implemented for the timer and the other two capture/compare blocks. The three interrupt events using the same vector are identified by an individual interrupt vector word. The interrupt vector word is used to add an offset to the program counter to continue the interrupt handler software at the corresponding program location. This simplifies the interrupt handler and gives each interrupt event the same overhead of 5 cycles in the interrupt handler.

UART

Serial communication is implemented by using software and one capture/compare block. The hardware supports the output of the

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 | 21 |