www.vxitech.com

EXAMPLES

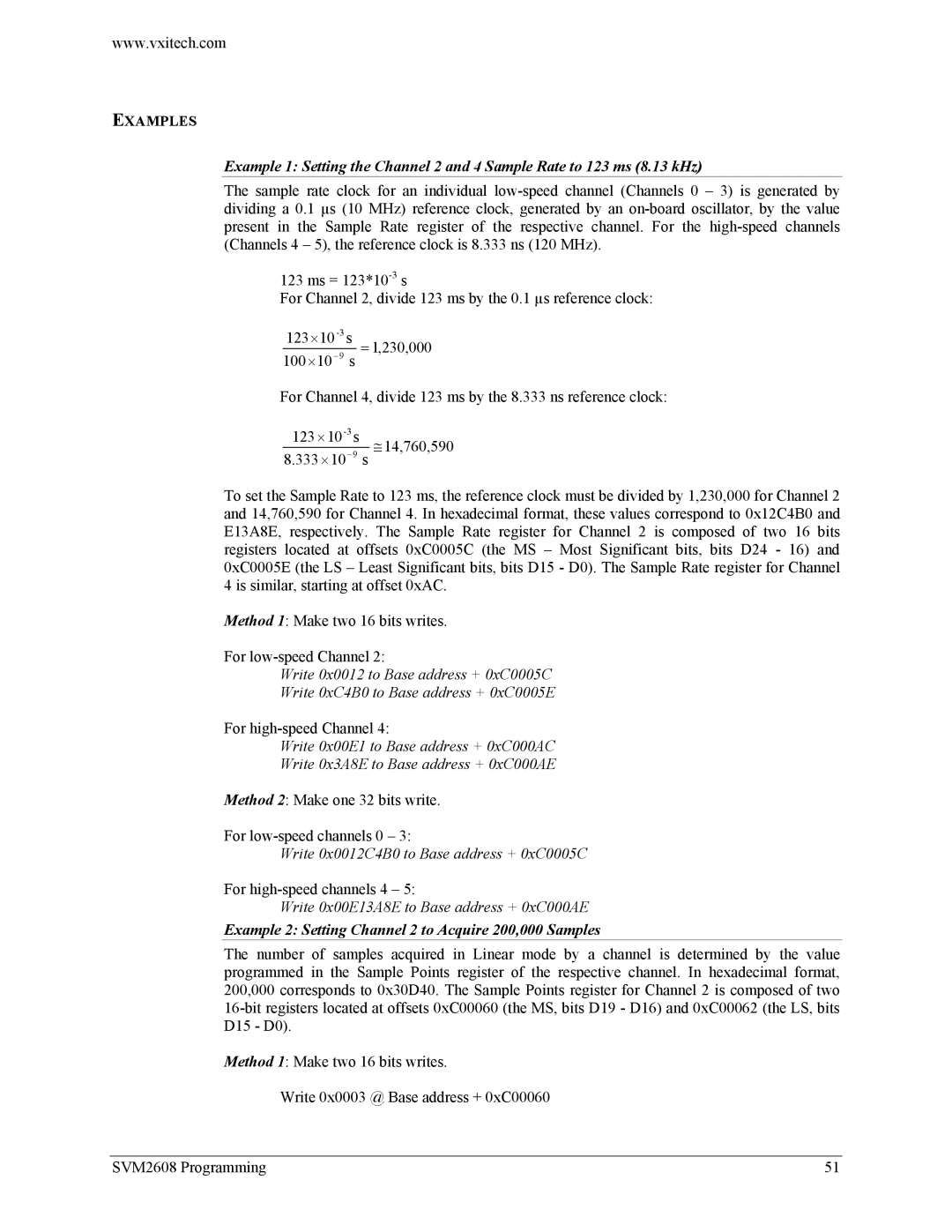

Example 1: Setting the Channel 2 and 4 Sample Rate to 123 ms (8.13 kHz)

The sample rate clock for an individual

123 ms =

For Channel 2, divide 123 ms by the 0.1 µs reference clock:

100⋅10−9 s

For Channel 4, divide 123 ms by the 8.333 ns reference clock:

123 ⋅ |

| ≅ 14,760,590 |

8.333 ⋅ 10−9 |

| |

s | ||

To set the Sample Rate to 123 ms, the reference clock must be divided by 1,230,000 for Channel 2 and 14,760,590 for Channel 4. In hexadecimal format, these values correspond to 0x12C4B0 and E13A8E, respectively. The Sample Rate register for Channel 2 is composed of two 16 bits registers located at offsets 0xC0005C (the MS – Most Significant bits, bits D24 - 16) and 0xC0005E (the LS – Least Significant bits, bits D15 - D0). The Sample Rate register for Channel 4 is similar, starting at offset 0xAC.

Method 1: Make two 16 bits writes.

For

Write 0x0012 to Base address + 0xC0005C

Write 0xC4B0 to Base address + 0xC0005E

For

Write 0x00E1 to Base address + 0xC000AC

Write 0x3A8E to Base address + 0xC000AE

Method 2: Make one 32 bits write.

For

Write 0x0012C4B0 to Base address + 0xC0005C

For

Write 0x00E13A8E to Base address + 0xC000AE

Example 2: Setting Channel 2 to Acquire 200,000 Samples

The number of samples acquired in Linear mode by a channel is determined by the value programmed in the Sample Points register of the respective channel. In hexadecimal format, 200,000 corresponds to 0x30D40. The Sample Points register for Channel 2 is composed of two

Method 1: Make two 16 bits writes.

Write 0x0003 @ Base address + 0xC00060

SVM2608 Programming | 51 |