Programmer’s Guide

Safety Information

Warranty

Limitation of Warranty

Contents

Programming Examples

Programming Command Cross-References

Contents

Contents

Contents

Contents

Contents

Contents

Contents

Contents

Agilent 8590/EMC Analyzers Programming Conversion Guide

Commands

Commands

Commands

Commands

Commands

Commands

Commands

Commands

Commands

Commands

Commands

Commands

Commands

Commands

Commands

Commands

Commands

Commands

Commands

Commands

Programming Fundamentals

Programming Fundamentals

Creating Valid Commands

Command Syntax Sample Valid Commands

Command Notation Syntax

Command TRIGGSequenceVideoLevel 2.5V is not valid because

Example TRIGgerSEQuenceVIDeoLEVel

Special Characters in Commands

Parameters indicates

Parameters in Commands

Example query SENSEFREQuencyCENTer? MAXimum

Variable Parameters

Block Program Data

Parameters in Commands

Disable the IF/Video/Sweep output ports

Turn off the display updates

Disable auto alignment

Improving Measurement Speed

Select phase noise performance

Use binary data format instead of Ascii

Minimize the number of Gpib transactions

Minimize DUT/instrument setup changes

Avoid unnecessary use of *RST

Putting Multiple Commands on the Same Line

Scpi Termination and Separator Syntax

Bad Command Good Command

Gpib Command Statements

Overview of Gpib Option A4H

Gpib Instrument Nomenclature

Overview of Gpib Option A4H

Handshake and Baud Rate

Settings for the Serial Interface

Overview of RS-232 Option 1AX

Character Format Parameters

Data Transfer Errors

Modem Line Handshaking

Printer Setup and Operation

Interconnection and Setup

Equipment

Unsupported printer, Printer Type set to None

Testing Printer Operation

Status Registers

Status Register System Simplified Block Diagram

What are the Status Registers?

Overall Status Register System Diagram

How Do You Access the Status Registers?

Common Command Access and Control

Status Subsystem Commands

Polling Method

Using the Service Request SRQ Method

Generating a Service Request

Example of Monitoring Conditions Using the STATus Command

Set INITiateCONTinuous off

Setting and Querying the Status Register

Details of Bits in All Registers

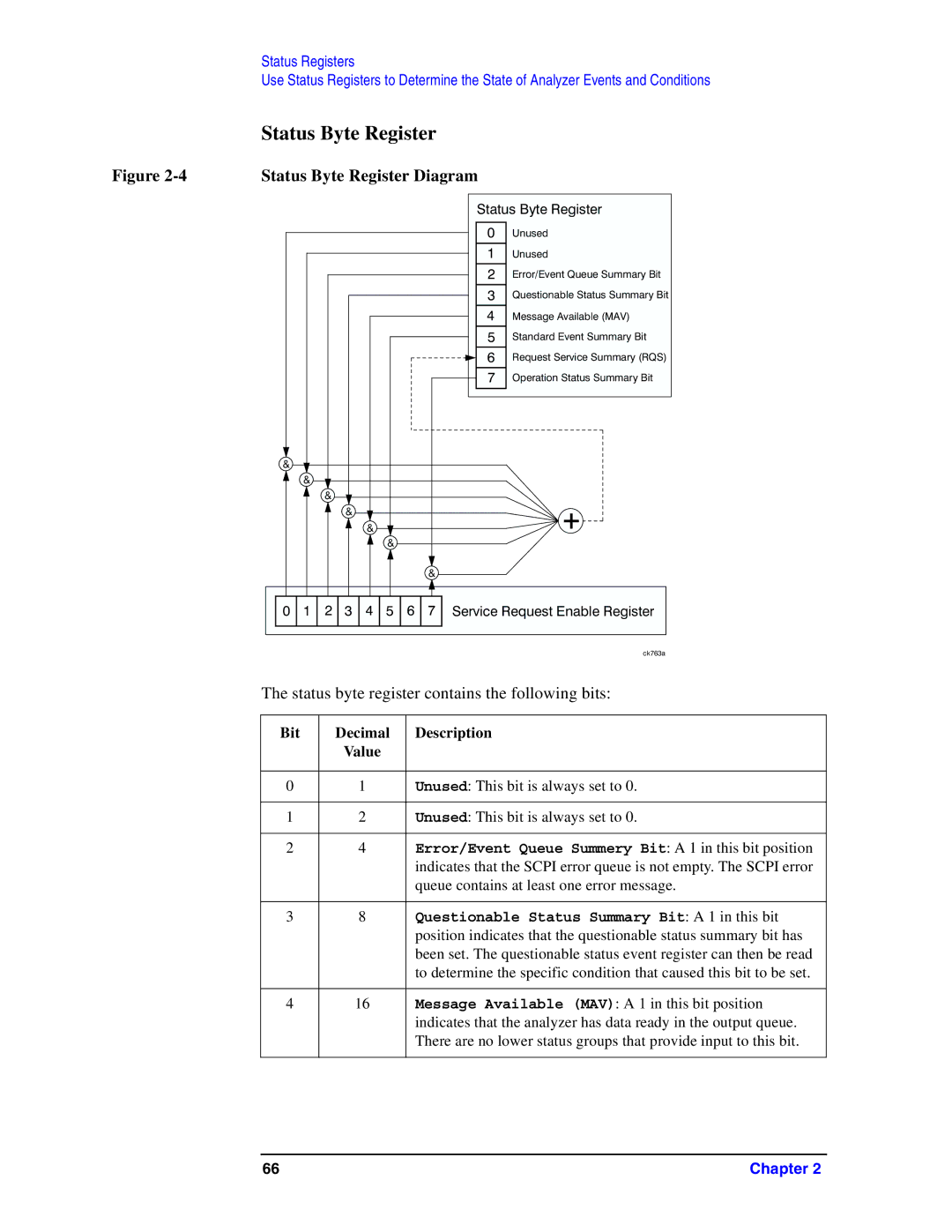

Status Byte Register Diagram

Status Byte Register

Service Request Enable Register

Standard Event Status Summary Bit a 1 in this bit

Service Request Enable Register

Service request enable register presets to zeros

Standard Event Status Register

Standard Event Status Register Diagram

Standard event status register contains the following bits

Standard Event Status Event Enable Register

Standard Event Status Event Enable Register

STATusOPERation Register

Status Operation Register Diagram

Always Zero

STATusOPERation Condition and Event Enable Registers

STATusOPERationEVENt? command

STATusQUEStionable Registers

STATusQUEStionableNTRansition num negative transition or

STATusQUEStionablePTRansition num positive transition where

STATusQUEStionableEVENt?

Status Questionable Register Diagram

INTregrity Sum Reserved Always Zero

STATusQUEStionablePOWer Register

Questionable Status Power Register Diagram

Questionable Status Event Enable Register

Questionable Status Event Enable Register

Questionable Status Power Condition and Event Registers

STATusQUEStionablePOWerEVENt?

Questionable Status Frequency Register Diagram

STATusQUEStionableFREQuency Register

That the synthesizer in the source tracking generator is

STATusQUEStionableFREQuency EVENt?

Questionable Status Calibration Register Diagram

STATusQUEStionableCALibration Register

Bit Decimal Description

Bit Decimal Description Value

Questionable Status Integrity Uncalibrated Register Diagram

STATusQUEStionableINTegrityUNCalibrated Register

Oversweep Meas Uncal a 1 in this position indicates

STATusQUEStionableINTegrityUNCalibratedNTRansition

STATusQUEStionableCALibration EVENt?

STATusQUEStionableINTegrityUNCalibratedCONDition?

STATusQUEStionableINTegrityUNCalibratedPTRansition

Questionable Status Integrity Register Diagram

STATusQUEStionableINTegrity Register

Data Uncalibrated Summary This is the summary

STATusQUEStionableINTegrityEVENt?

Chapter

Programming Examples

List of Programming Examples

Programming Examples System Requirements

Programming Examples using VTL

Typical Example Program Contents

ViPrintf

Linking to VTL Libraries

Compiling and Linking a VTL Program

Bit Applications assumes Windows 95 operating system

Bit Applications

Example Program

Including the Visa Declarations File

#include visa.h

Opening a Session

Device Sessions

Chapter 101

Addressing a Session

Interface Syntax

Closing a Session

GPIB-VXI024

Using Marker Peak Search and Peak Excursion

Example

Chapter 105

106

Chapter 107

Using Marker Delta Mode and Marker Minimum Search

Chapter 109

110

Chapter 111

Performing Internal Self-alignment

E740xA EMC Analyzers

Chapter 113

114

Chapter 115

Reading Trace Data using Ascii Format Gpib

Calsour Stat on

Chapter 117

118

Chapter 119

Reading Trace Data Using 32-bit Real Format Gpib

Chapter 121

122

Chapter 123

124

Reading Trace Data Using Ascii Format RS-232

126

Chapter 127

128

Chapter 129

Reading Trace Data Using 32-bit Real Format RS-232

Calculate the number of bytes in the trace record

Chapter 131

132

Chapter 133

134

Using Limit Lines

CALCLLINE1CONTDOM Freq CALCLLINE1TYPE UPP CALCLLINE1DISP on

136

Chapter 137

138

Chapter 139

140

Measuring Noise

142

Chapter 143

144

Entering Amplitude Correction Data

Enter amplitude correction frequency/amplitude pairs

146

Chapter 147

148

Status Register-Determine When a Measurement is Done

Initimm OPC?

150

Chapter 151

152

Chapter 153

154

Determine if an Error has Occurred

Sensfreqcent 500 MHZ Sensfreqspan 100 MHZ

156

Chapter 157

158

Chapter 159

160

Measuring Harmonic Distortion Gpib

162

Chapter 163

164

Chapter 165

166

Chapter 167

168

Measuring Harmonic Distortion RS-232

170

Chapter 171

172

Chapter 173

174

Chapter 175

176

Making Faster Measurements multiple measurements

IDN?

178

Chapter 179

180

Chapter 181

182

Chapter 183

184

Programming Command

Functional Index to Scpi Subsection

Bandwidth

Programming Command Cross-References

188

Language Reference

Commands for Use with ANSI/IEEE Std 488.1-1987. New York, NY

Scpi Sections and Subsections

Scpi Subsystem/Subsection

192

Calibration Query

Ieee Common Commands

Standard Event Status Enable

Clear Status

Instrument State Query

Standard Event Status Register Query

Identification Query

#PQQQSYSTSET #NMMMstatedata

Operation Complete

Query Instrument Options

Recall

Save

Reset

Service Request Enable

Read Status Byte Query

Trigger

Self Test Query

Wait-to-Continue

ABORt Subsystem

Abort

ABORt

NdBresults

CALCulate Subsystem

NdBpoints

CALCulateBWIDthBANDwidthRESult?

NdBstate

Calculate Correction at Frequency

Test Current Trace Data Against all Limit Lines

Add Measure to List

Append Signal Data to List

CALCulateEMISLISt Subsection

Add Marker to List

Field Description Table

CALCulateEMISLIStADD 1e6 or

Detailed Field Descriptions

Clear Marks

CALCulateEMISLIStCLEar ALLCURRentinteger

Set Comment for Marked Signals

Set Comment for Signals

Set Comment for Current Signal

Delete Signal

Retrieve Signals in List

Turn Signal List On or Off

Retrieve Signal as a String

Mark Selected Signals

Position Cursor to Signal List

Specify Sort Key

CALCulateEMISLIStSELect FIRStLASTNEXTPREVious integer

Specify Signal List Display Parameters

Control Limit Line Amplitude Interpolation

CALCulateLLINe Subsection

Delete All Correction Sets in Memory

Set Fixed or Relative Limit Lines

Set Limit Line X-axis Units

Control Limit Line Frequency Interpolation

Define Limit Line Values

Example CALCLLIN1DATA 1000000000,-20,0,200000000,-30,1

Fi + yi

Connected 0 or

Display the Limit Line

Merge Additional Values into the Existing Limit Line

Delete Limit Line

CALCulateLLINe12DELete

Display the Limit Margin

Test the Data Against the Limit Line

Set the Margin Size

CALCulateLLINe12FAIL?

CALCulateLLINe12STATe OFFON01 CALCulateLLINe12STATe?

Control Limit Line Testing

Select the Type of Limit Line

CALCulateLLINe12TYPE UPPerLOWer CALCulateLLINe12TYPE?

Markers All Off on All Traces

Frequency Counter Marker Resolution

CALCulateMARKer Subsection

Continuous Peaking Marker Function

Frequency Counter Marker Query

Frequency Counter Marker Automatic Resolution

Frequency Counter Marker

Marker Function

Marker Peak Maximum Search

Marker Peak Maximum Left Search

Marker Next Peak Maximum Search

Marker Peak Minimum Search

Marker Mode

Marker Peak Maximum Right Search

CALCulateMARKer1234MAXimumRIGHt

Define Peak Excursion

Define Peak Search

Set Center Frequency to the Marker Value

Define Peak Threshold

Peak to Peak Delta Markers

Set Reference Level to the Marker Value

Set Center Frequency Step Size to the Marker Value

Set Span to the Marker Value

Set Start Frequency to the Marker Value

Set Stop Frequency to the Marker Value

Marker to Trace

Continuous Signal Tracking Function

Marker Table On/Off

Marker to Trace Auto

Marker X Position

Marker X Value

Span Markers Center Frequency X Value

CALCulateMARKer1234X param CALCulateMARKer1234X?

Span Markers Center Frequency X Position

Span Markers Span X Position

Delta Pair Markers Start Frequency X Position

Span Markers Span X Value

Delta Pair Markers Stop Frequency X Position

Marker X-Axis Readout

CALCulateMARKer1234XSPAN param CALCulateMARKer1234XSPAN?

Delta Pair Markers Start Frequency X Value

Delta Pair Markers Stop Frequency X Value

Marker Read Y Value

CALCulateNTData Subsection

Normalize the Trace Data

CALCulateNTDataSTATe OFFON01 CALCulateNTDataSTATe?

Align All Instrument Assemblies

Set Auto Align Mode All or Not RF

CALibration Subsystem

CALibrationALL CALibrationALL?

Align FM Demodulation

Return to the Default Alignment Data

Automatic Alignment

Query the Internal or External Frequency Reference

Select the Frequency Corrections

Coarse Adjust the Frequency Reference

Fine Adjust the Frequency Reference

Align the RF Circuitry

CALibrationSOURceSTATe OFFON01 CALibrationSOURceSTATe?

Select the Source State for Calibration

Calibrate the Tracking Generator

CALibrationTG CALibrationTG?

COUPle the Function to Other Settings

COUPle Subsystem

COUPle Allnone COUPle?

Sweep points

Date and Time Display Format

DISPlay Subsystem

Display Viewing Angle

Date and Time Display

Turn the Entire Display On/Off

DISPlayENABle OFFON01

Display Annotation Title Data

Turn the Full Screen Display On/Off

Trace X-Axis Scale Offset

Window Annotation

Trace Graticule Display

Log SENSeSWEepSPACing LINearLOGarithmic

If Gain Auto/Reference Level Auto Ranging

Display Line Amplitude

Display Line On/Off

DISPlayWINDowTRACeYDLINe ampl DISPlayWINDowTRACeYDLINe?

See command CALCulateNTDataSTATe OFFON01

Normalized Reference Level

Normalized Reference Level Position

Trace Y-Axis Amplitude Scaling

Trace Y-Axis Frequency Scaling

Trace Y-Axis Reference Level

Trace Y-Axis Reference Level Offset

DISPlayWINDowTRACeYSCALeRLEVelOFFSet

Relampl

Vertical Axis Scaling

Numeric Data format

FORMat Subsystem

Byte Order

FORMatBORDer NORMalSWAPped FORMatBORDer?

Ascii

Abort the Print

Select Report Content

HCOPy Subsystem

Printer Type

Color Hard Copy

Select a Signal List to Include in a Report

Select a Signal List to Include in a Report Delta

HCOPyIMAGeCOLorSTATe OFFON01 HCOPyIMAGeCOLorSTATe?

Orientation

Print a Hard Copy

Form Feed the Print Item

Number of Items Printed on a

Printed Page Size

Select Report Type

HCOPyREPOrtTYPE SCREenREPort

INITiate Subsystem

Continuous or Single Measurements

INITiateCONTinuous OFFON01 INITiateCONTinuous?

Take New Data Acquisitions

Abort Measurement

Pause the Measurement

INITiateRESTart

Restart the Measurement

Resume the Measurement

INITiateRESume

INPutCOUPling Acdc INPutCOUPling?

INPut Subsystem

Input Port Coupling

Selecting Input Coupling

Clear the Input Overload

INPutPROTectionCLEar

MEASure Group of Commands

Configure Commands

CONFiguremeasurement

FETChmeasurementn?

Fetch Commands

Measure Commands

MEASuremeasurementn?

Read Commands

Measurement Group of Commands

READmeasurementn?

Read Command

Configure for Measuring Frequency

Get Measurement Results

Measure at Marker and Add to List

Setting Max/Min On or Off

Measure at Marker

Max/Min View -Max

Remeasure Current Signal

CONFigureEMIPEAKs MEASureEMIPEAKs?

Measure Peaks

MMEMory Subsystem

Catalog the Selected Memory Location

Copy a File

Load a Corrections Table from a File

Move Data to File

Delete a File

Load a Limit Line from Memory to the Instrument

Load an Instrument State from a File

Load a Trace From a File to the Instrument

Store Load/Save a Signal List

Make a Directory

MMEMoryRDIRectory dirname

Delete a Directory

Store a Corrections Table to a File

MMEMorySTOReCORRection ANTennaCABLeOTHerUSER,filename

Store a Screen Image in a Graphic File

Store a Limit Line in a File

Store Measurement Results in a File

Store an Instrument State in a File

Store a Trace in a File

MMEMorySTOReTRACe label,filename

Mmemstortrac TRACE3,Cmytrace.trc

OUTPut Subsystem

Turn Output On/Off

OUTPutSTATe OFFON01 OUTPutSTATe?

SENSe Subsystem

Set the Average Count

SENSeAVERage Subsection

Clear the Current Average

Turn Averaging On/Off

Turn Automatic Averaging On/Off

SENSeAVERageTYPEAUTO OFFON01 SENSeAVERageTYPEAUTO?

Auto Rules for Average Type

Type of Averaging for Measurements

SENSeAVERageTYPE VIDeoRMS

SENSeAVERageTYPE?

Resolution Bandwidth Mode

Resolution Bandwidth

Resolution Bandwidth Automatic

SENSeBANDwidth Subsection

Video Bandwidth

Video to Resolution Bandwidth Ratio

Video to Resolution Bandwidth Ratio Mode Select

Video Bandwidth Automatic

VBW and RBW Ratio Auto Rules

Resolution Bandwidth Type

SENSeBANDwidthTYPE IMPulseDB6DB3 SENSeBANDwidthTYPE?

Perform Amplitude Correction

SENSeCORRection Subsection

Delete All Corrections

Set Amplitude Correction Data

SENSeCORRectionCSET1234DATAMERGe freq,relampl,freq,relampl

Set Amplitude Correction Frequency Interpolation

SENSeCORRectionCSETALLSTATe must be on for this command to

Delete Amplitude Correction

SENSeCORRectionCSET1234DELete

Input Impedance Correction

External Amplifier Correction

FM Deviation

SENSeDEMod Subsection

Type of Demodulation

Squelch

Demodulation Control

Demod Time

Demod View

SENSeDETector Subsection

Automatic Detection Type Selected

SENSeDETectorAUTO OFFON01 SENSeDETectorAUTO?

Auto Rules of Detector Selection

NEGativePOSitiveSAMPleAVERageRMS

Type of Detection

SENSeDETectorFUNCtion

SENSeDETectorFUNCtion?

Type of EMI Detector

Unrange

EMI View

Range Immediate

SENSeDETectorRANGeIMMediate

Auto Measure Peak On or Off

SENSeEMI Subsection

Auto Measure Average On or Off

Auto Measure Quasi Peak On or Off

Setting the Dwell Time for Average Peak

Setting the Dwell Time for Peak

Setting the Dwell Time for Quasi Peak

Preselector Centering On or Off E7403A, E7404A, E7405A only

Setting the Dwell Time for Range

Auto Measure Margin On or Off

SENSeEMIMEASureRANGeDWELltime SENSeEMIMEASureRANGeDWELl?

SENSeFREQuency Subsection

Center Frequency

Center Frequency Step Size Automatic

Center Frequency Step Size

Frequency Span

SENSeFREQuencySPAN freq SENSeFREQuencySPAN?

Full Frequency Span

Last Frequency Span

Start Frequency

SENSeFREQuencySTOP freq SENSeFREQuencySTOP?

Frequency Synthesis Mode

Stop Frequency

SENSeFREQuencySYNThesis SENSeFREQuencySYNThesis?

Frequency Synthesis State

Input Attenuation

SENSePOWer Subsection

Enable/Disable QPD X10 Gain

Input Port Attenuator Auto

SENSePOWerRFGAINSTATe OFFON01 SENSePOWerRFGAINSTATe?

Input Port Power Gain

Input Port Maximum Mixer Power

SENSePOWerRFPADJust freq SENSePOWerRFPADJust?

SENSePOWerRFPCENter

Preselector Center

SENSeSWEep Subsection

Sweep Points

Set Frequency Domain Scale Type

SENSeSWEepTIME time SENSeSWEepTIME?

Sweep Time

Automatic Sweep Time

SENSeSWEepTIMEAUTO OFFON01 SENSeSWEepTIMEAUTO?

SENSeSWEepTIMEGATEDELay time SENSeSWEepTIMEGATEDELay?

Sweep Time Mode

Time Gating Delay Option 1D6 Only

Time Gate Length Option 1D6 Only

Time Gate Polarity Option 1D6 Only

Preset Time Gate Option 1D6 Only

Time Gate Level Option 1D6 Only

Control Time Gate Option 1D6 Only

Time Gate Trigger Type Option 1D6 Only

SENSeSWEepTIMEGATETYPE LEVelEDGE SENSeSWEepTIMEGATETYPE?

Sets the Output Power Offset Correction

SOURce Subsystem

Source Attenuation

SOURcePOWerATTenuationAUTO?

Sets the Output Power

SOURcePOWerATTenuationAUTO OFFON01

Automatic Source Attenuation

SOURcePOWerMODE FIXedSWEep SOURcePOWerMODE?

Sets the Source Output Power Mode

Set the Source Sweep Power Range

SOURcePOWerSPAN relampl SOURcePOWerSPAN?

Set the Output Power at the Start of the Sweep

Set the Output Power to Step Automatically

Set the Output Power Step Size

SOURcePOWerSWEep relampl SOURcePOWerSWEep?

Output Power Tracking

Output Power Tracking Peak

SOURcePOWerTRCKing integer SOURcePOWerTRCKing?

Operation Condition Query

Operation Enable

STATus Subsystem

Operation Event Query

Operation Negative Transition

Preset the Status Byte

STATusPRESet

Operation Positive Transition

Questionable Calibration Condition

Questionable Calibration Enable

STATusQUEStionable Subsection

Questionable Calibration Event Query

Questionable Condition

Questionable Calibration Negative Transition

Questionable Calibration Positive Transition

STATusQUEStionableCONDition?

Questionable Event Query

Questionable Enable

STATusQUEStionableENABle integer STATusQUEStionableENABle?

Questionable Frequency Condition

Questionable Frequency Negative Transition

Questionable Frequency Enable

Questionable Frequency Event Query

STATusQUEStionableFREQuencyEVENt?

Questionable Integrity Condition

Questionable Integrity Enable

Questionable Frequency Positive Transition

Questionable Integrity Event Query

Questionable Integrity Uncalibrated Enable

Questionable Integrity Negative Transition

Questionable Integrity Positive Transition

Questionable Integrity Uncalibrated Positive Transition

Questionable Integrity Uncalibrated Event Query

Questionable Integrity Uncalibrated Negative Transition

Integer STATusQUEStionableINTegrityUNCalibratedNTRansition?

Questionable Power Event Query

Questionable Power Condition

Questionable Power Enable

STATusQUEStionablePOWerCONDition?

Questionable Power Negative Transition

Questionable Power Positive Transition

Questionable Positive Transition

Serial Port DTR Setup

SYSTem Subsystem

Gpib Address

Serial Port RTS Setup

Serial Port Baud Rate Setup

Hardware Configuration Query

Serial Port Receive Pace Setup

Serial Port Transmit Pace Setup

Display the Hardware Configuration

Error Information Query

System Configuration Query

Display System Configuration

Set Date

Host Identification Query

Locate Scpi Command Errors

SYSTemERRorVERBose OFFON01 SYSTemERRorVERBose?

First set SYSTERRVERBose on

License Key Install Application/Option

Delete a License Key

Power On Type

Power On Elapsed Time

Power On Time

Enable IF/Video/Sweep Output Ports

Preset

Persistent State Reset

Preset Type

Set Time

Save User Preset

Speaker Control

Scpi Version Query

Transfer Trace Data

TRACe Subsystem

Copy Trace

TRACeCOPY sourcetrace,desttrace

Commands Mmemstortrac and Mmemloadtrac are

Tracdata TRACE1,#41604binary trace

DataLF-EOI

Query Number of Peaks Found

Query the Signal Peaks

Mean Trace Data

Peak Sorting

Smoothing With 401 Trace Points and 31 Smoothing Points

Number of Points for Smoothing

Trace Math Subtract

TRACeMATHSMOothPOINts integer TRACeMATHSMOothPOINts?

TRACeMATHSUBTractDLINe trace

Select Trace Display Mode

Trace Math Subtract From Display Line

Example Tracmathsubtdlin TRACE1

TRIGgerSEQuenceDELay delay TRIGgerSEQuenceDELay?

External Trigger, Line Trigger Delay Value

External Trigger, Line Trigger Delay Enable

TRIGger Subsystem

Trigger Offset

Trigseqoffs 1.0s

Trigger Source

Video Trigger Level Amplitude

TRIGgerSEQuenceVIDeoLEVelFREQuency?

Video Trigger Level Frequency

TRIGgerSEQuenceVIDeoLEVelFREQuency freq

TRIGgerSEQuenceVIDeoLEVel ampl

Select Power Units of Measure

UNITPOWer Dbmdbmvdbuvdbuavwa UNITPOWer?

Unit Subsystem

Agilent 8590/EMC Analyzers

Guide here, Agilent Part Number E7401-90035

Index

342

Index 343

344

Index 345

346

Index 347

348

Index 349